# UNIVERSITY OF CALIFORNIA

### Santa Barbara

Micro Power Delta-Sigma Analog-to-Digital Converters based on Novel Self-Biased

Inverter Amplifiers

A Dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Le Wang

Committee in charge:

Professor Luke Theogarajan, Chair

Professor Kwang-Ting Cheng

Professor Forrest Brewer

Professor Stephen Long

Dr. Michael Perrott

December 2010

# The dissertation of Le Wang is approved.

| Michael Perrott                   |  |

|-----------------------------------|--|

|                                   |  |

| Stephen Long                      |  |

|                                   |  |

| Forrest Brewer                    |  |

|                                   |  |

| Kwang-Ting Cheng                  |  |

|                                   |  |

| Luke Theogarajan, Committee Chair |  |

September 2010

| Micro Power Delta-Sigma Analog-to-Digital Converters based on Novel Self-Biased |

|---------------------------------------------------------------------------------|

| Inverter Amplifiers                                                             |

Copyright © 2010

by

Le Wang

### **ACKNOWLEDGEMENTS**

The dissertation belongs to many people who have directly or indirectly helped me achieve this goal. First, I sincerely appreciate my advisor, Prof. Luke Theogarajan, for his consistent financial and technical support in my research work at UCSB. His detailed and wholehearted guidance made the project progressing smoothly, and my academic endeavors here turned out to be very enjoyable and fruitful.

I would like very much to thank Prof. Forrest Brewer, Tim Cheng, Steve Long, and Michael Perrott for their time and kindness serving in my program committee. In addition, I am very thankful to Prof. Perrott for his prompt technical feedbacks and kind help on my career search. I also appreciate Prof. Brewer's interest in my research work and all the valuable discussions.

I gained great knowledge and insights from the courses offered by Prof. Forrest Brewer, Steve Long, Luke Theogarajan, Umesh Mishra, and Mark Rodwell. I highly enjoyed those courses.

In addition, I am truly grateful to the ECE department at UCSB for offering me several TA positions and the dissertation fellowship, which greatly helped me completing the program. I am also thankful to Val de Veyra, Paul Gritt, and many others in the department for their great assistance in my student life.

I would also like to thank all the current and previous members, too many to name, of the Biomimetic group for working together and a lot of fun that made my UCSB experience unforgettable.

Finally, I would like to deeply appreciate my whole family for their unconditional support and all the encouragements.

#### VITA OF LE WANG

# July 2010

#### **EDUCATION**

Doctor of Philosophy in Electrical Engineering, University of California, Santa Barbara, September 2010

Master of Science in Electrical Engineering, Washington State University, Pullman, July 2006

Bachelor of Science in Electrical Engineering, Nanjing University, China, June 2001

#### **PUBLICATIONS**

"A Micro Power Delta-Sigma Modulator based on a Self-Biased Fully Differential Super Inverter for Neural Recording," *Custom Integrated Circuit Conference*, San Jose, Sept. 2010.

"Energy Efficient 136 Mb/s OOK Implantable Transmitter for Wireless Brain Computer Interface," *International Microwave Symposium*, Anaheim, May 2010

"Highly Linear KU-Band SiGe PIN Diode Phase Shifter in Standard SiGe BiCMOS Process," *Microwave and Wireless Component Letter*, vol. 20, no. 1, Jan. 2010.

"On-Wafer Wireless Testing and Mismatch Monitoring Using RF Transmitters with Integrated Antennas," *Radio Frequency Integrated Circuits*, Boston, June 2009

"A 5.3 GHz Low-Phase-Noise LC VCO with Harmonic Filtering Resistor," *International Symposium on Circuit and System*, Greece, May 2006.

"A 15-GHz Single-Pole Double-Throw Annular MOSFET Switch for Space Applications," *Workshop on Microelectronics and Electron Device*, Boise, April 2005

### PROFESSIONAL EMPLOYMENT

2002-2004: ASIC Design Engineer, Arcadia Design Systems Inc., Shanghai

#### **AWARDS**

ECE Dissertation Fellowship, University of California, Santa Barbara, 2010

Best Poster Award, Center for Design of Analog-Digital Integrated Circuits, 2006

Best Poster Award, Workshop on Microelectronics and Electron Devices, 2005

### **ABSTRACT**

Micro Power Delta-Sigma Analog-to-Digital Converters based on Novel Self-Biased

Inverter Amplifiers

by

### Le Wang

This dissertation work presents the design and implementation of micro power switched-capacitor delta-sigma analog-to-digital converters for neural recording systems. Novel self-biased fully differential inverter amplifiers are proposed to replace conventional operational amplifiers for achieving high power and area efficiency. By responding to differential-mode and common-mode signals in different ways, the proposed inverter amplifiers show high differential-mode gain and common-mode rejection, which are advantageous compared to a pseudo-differential input pair. The operation principles and analytical models of the inverter amplifiers will be discussed in the dissertation. To realize inverter amplifier-based switched-capacitor integrators, a floating sampling scheme is devised to decouple the nominal input common-mode voltage and the input DC biasing voltage of the inverter amplifiers, mitigating the limited input CM range. The floating sampling scheme eliminates the need for generating accurate on-chip voltage references by self-referencing the sampling and

integration processes. For the implementation of multi-stage noise-shaping architectures, a floating correlated double sampling technique is proposed by interleaving two sets of capacitors in the switched-capacitor integrator to improve the gain-linearity performance of the inverter amplifiers.

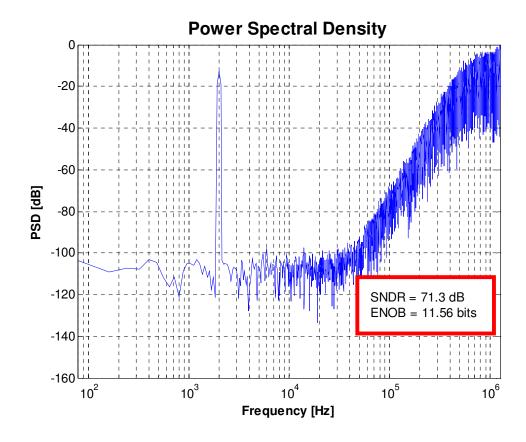

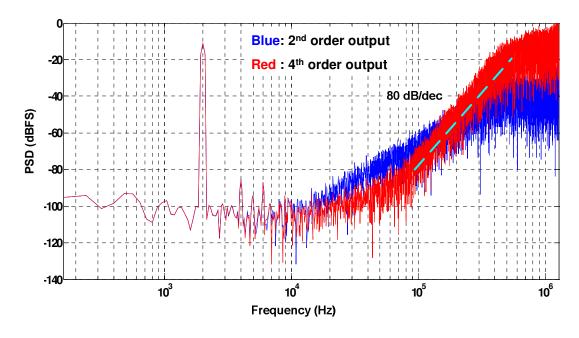

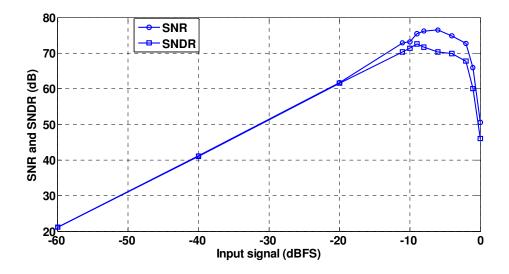

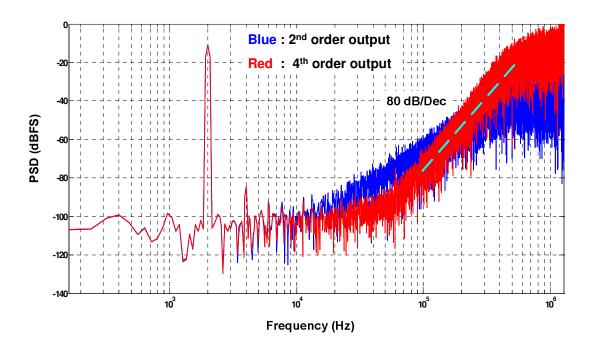

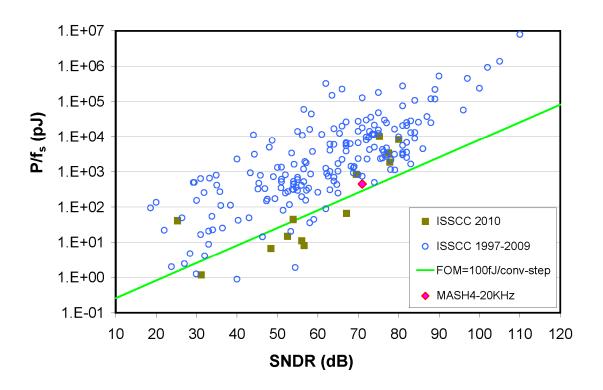

Several 4<sup>th</sup>-order inverter amplifier-based MASH prototypes with/without the CDS circuit were implemented in a 0.13  $\mu$ m CMOS process. The CDS-enhanced MASH prototype achieves 71 dB peak SNDR over 20 KHz signal bandwidth, and consumes 18 $\mu$ W power from a 1.5 V supply. The 2<sup>nd</sup>-order delta-sigma modulator of the first stage achieves 73 dB peak SNDR over 10 KHz signal bandwidth, and consumes 10 $\mu$ W power. The results demonstrates the power efficiency and design flexibility of the inverter amplifier-based design methodologies, which can also be extended for other low power, low cost, and high yield IC applications.

# TABLE OF CONTENTS

| I. INTRODUCTION                       |

|---------------------------------------|

| A. Motivation                         |

| B. Organization7                      |

| II. OVERVIEW of DELTA-SIGMA ADC       |

| A. Delta-Sigma Modulator9             |

| 1. First order loop dynamics          |

| 2. Higher order loop dynamics         |

| B. Decimation Filter 20               |

| III. CIRCUIT CONSIDERATIONS           |

| A. Opamp Nonidealities                |

| 1. Finite gain effect                 |

| 2. Settling time                      |

| 3. Gain nonlinearity                  |

| B. Noise Sources                      |

| 1. Thermal noise                      |

| 2. Clock jitter                       |

| C. Distortion Sources                 |

| 1. Mismatch in the differential paths |

| 2. Even-order harmonic distortion     |

| 3. Nonideal switches                  |

| IV. SYSTEM CONSIDERATIONS              |

|----------------------------------------|

| A. Delta-Sigma versus Nyquist-Rate     |

| B. Discrete-Time versus Continous-Time |

| C. Single-Loop versus MASH54           |

| D. Single-Bit versus Multi-Bit57       |

| F. Opamp versus Inverter Amplifier     |

| V. CIRCUIT INNOVATIONS                 |

| A. The Super Inverter62                |

| 1. Operation principles63              |

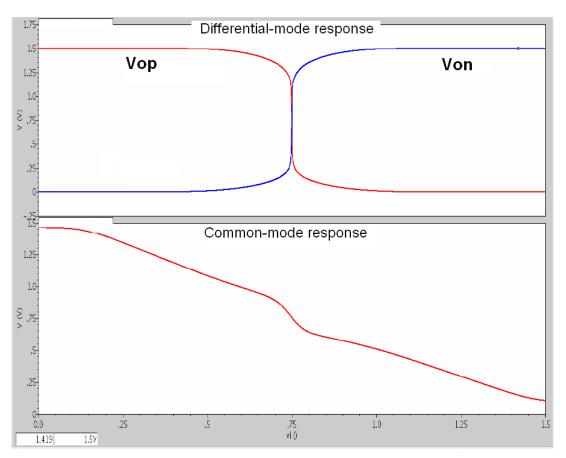

| 2. Simulation results                  |

| B. The New Inverter                    |

| 1. Operation principles                |

| 2. Simulation results                  |

| 3. High-gain topology                  |

| B. Floating CDS89                      |

| 1. Floating sampling scheme91          |

| 2. The CDS topology                    |

| 3. Performance evaluation              |

| VI. CHIP IMPLEMENTATION                |

| A. System Level Design                 |

| 1. Simulink models98                   |

| 2. Choice of the modulator parameters  |

| B. Circuit Level Design   | 103 |

|---------------------------|-----|

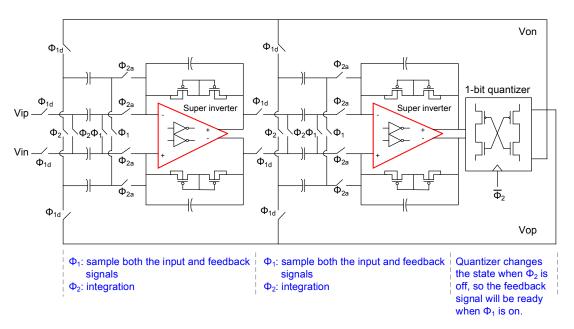

| 1. Second-order modulator | 103 |

| 2. Pseudo-resistor        | 105 |

| 3. Quantizer              | 107 |

| 4. Clock generator        | 108 |

| 5. MASH architectures     | 109 |

| C. Mask Layout Design     | 113 |

| 1. General considerations | 113 |

| 2. Layout views           | 114 |

| VII. CHIP MEASUREMENT     | 116 |

| A. Test Environment Setup | 116 |

| B. Measurement Results    | 118 |

| 1. Second-order modulator | 118 |

| 2. MASH prototypes        | 122 |

| VIII. CONCLUSION          | 132 |

| A. Summary                | 132 |

| B. Future Work            | 133 |

| References                | 134 |

| Annandiy                  | 130 |

# LIST OF FIGURES

| Figure 1.1 System diagram of the high density neural implant                         |

|--------------------------------------------------------------------------------------|

| Figure 2.1 System diagram of the 1 <sup>st</sup> order delta-sigma modulator         |

| Figure 2.2 ADC transfer curve and the quantization error                             |

| Figure 2.3 Quantization noise waveform and in-band power spectral density 12         |

| Figure 2.4 Nyquist rate sampling versus oversampling                                 |

| Figure 2.5 Power spectral density of an oversampling ADC                             |

| Figure 2.6 Simplified model of the 1 <sup>st</sup> order delta-sigma modulator       |

| Figure 2.7 Power spectral density of the 1 <sup>st</sup> order delta-sigma modulator |

| Figure 2.8 Simplified model of the 2 <sup>nd</sup> order delta-sigma modulator       |

| Figure 2.9 Transfer curve of a single-bit quantizer                                  |

| Figure 2.10 Maximum SNR versus OSR                                                   |

| Figure 2.11 Running-average filter with M=8                                          |

| Figure 2.12 Part of the Decimation filter – Sinc <sup>L+1</sup> FIR filter           |

| Figure 3.1 A delaying switched-capacitor integrator                                  |

| Figure 3.2 Root locus of the 1 <sup>st</sup> order NTF                               |

| Figure 3.3 Frequency response of the 1 <sup>st</sup> order NTF                       |

| Figure 3.4 Two-stage MASH architecture                                               |

| Figure 3.5 OPAMP gain effects on the 4 <sup>th</sup> order MASH                      |

| Figure 3.6 Three settling processes for different input steps                        |

| Figure 3.7 Small-signal model of a capacitive-feedback amplifier                     |

| Figure 3.8 Three settling regions in terms of the nominal output voltage         | 32   |

|----------------------------------------------------------------------------------|------|

| Figure 3.9 Typical amplifier transfer characteristics.                           | 33   |

| Figure 3.10 SNR degradation and the effective amplifier gain                     | 34   |

| Figure 3.11 Modeling the amplifier gain nonlinearity in a delaying SC integrator | 36   |

| Figure 3.12 Noise budget of the delta-sigma modulator                            | 37   |

| Figure 3.13 Small-signal models for thermal noise calculation                    | 38   |

| Figure 3.14 Noise folding during the sampling phase                              | 39   |

| Figure 3.15 KT/C noise versus quantization noise                                 | 41   |

| Figure 3.16 Sampling diagram with clock jitter                                   | 44   |

| Figure 3.17 Input sampling circuitry of SC circuits                              | 49   |

| Figure 3.18 Conductance of a transmission gate switch                            | 50   |

| Figure 4.1 Zodiac of ADC architectures                                           | 52   |

| Figure 4.2 Circuit diagram of the continuous-time delta-sigma modulator          | 53   |

| Figure 4.3 Current-biased Opamp versus voltage-biased inverter amplifier         | 59   |

| Figure 4.4 Current and voltage responses of an inverter amplifier                | 60   |

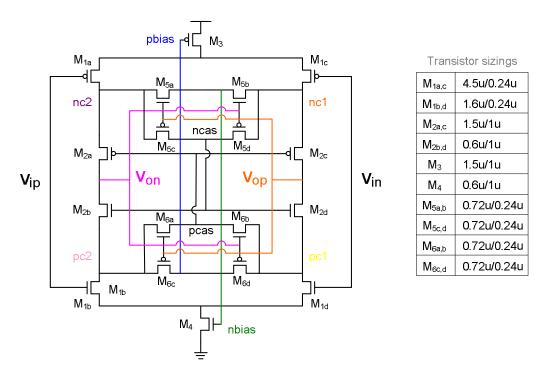

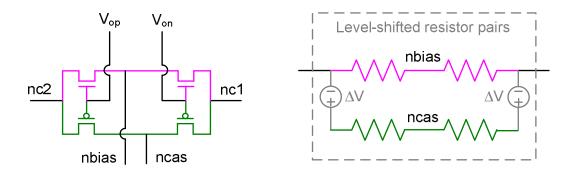

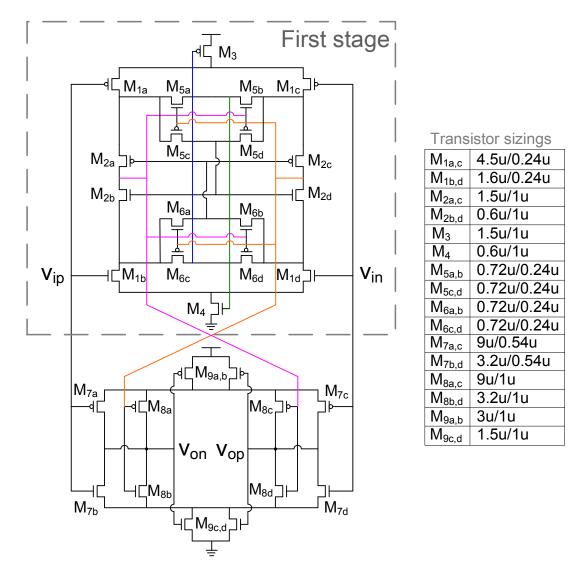

| Figure 5.1 Circuit diagram of the super inverter                                 | 64   |

| Figure 5.2 Simplified small-signal models highlighting the degeneration stages   | 65   |

| Figure 5.3 Simplified small-signal models highlighting the cascode stages        | 67   |

| Figure 5.4 Positive feedback loops in the super inverter                         | 68   |

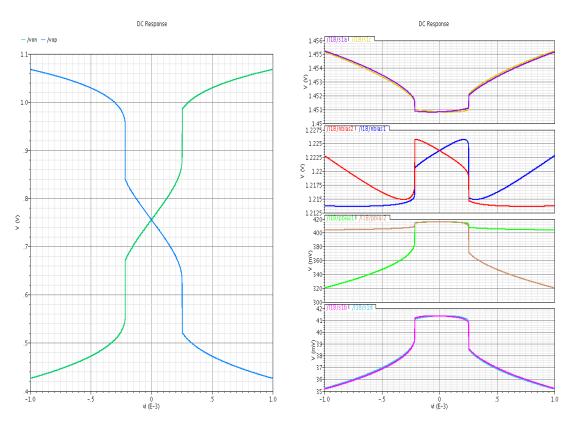

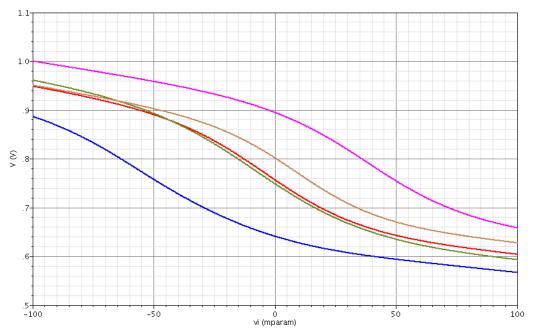

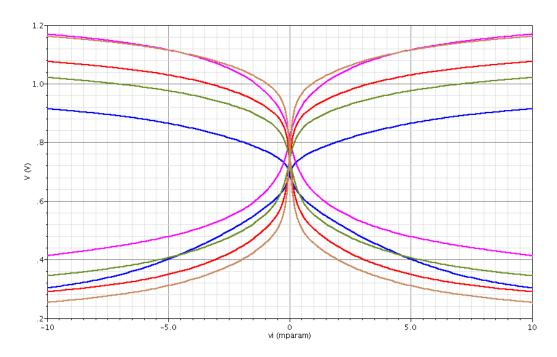

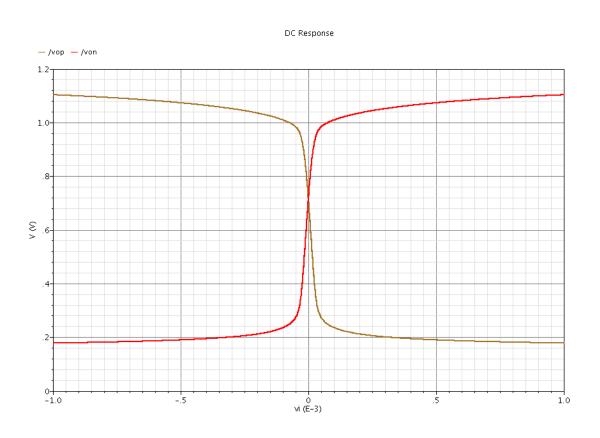

| Figure 5.5 DC transfer curves of the super inverter                              | 71   |

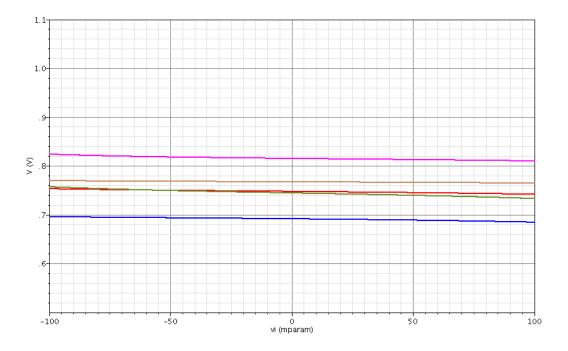

| Figure 5.6 Zoom-in view of the DC response                                       | 72   |

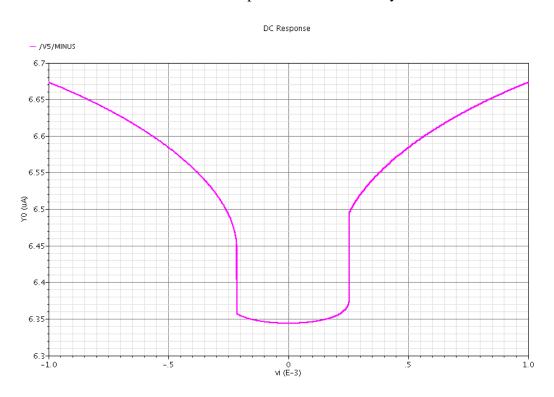

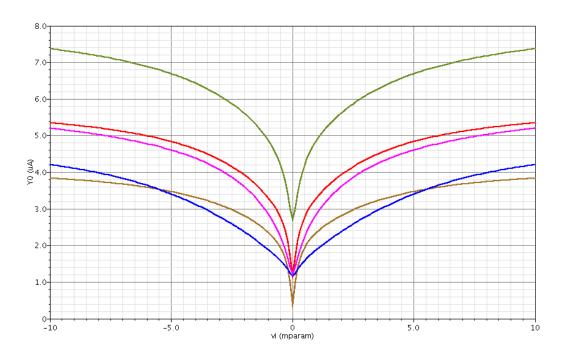

| Figure 5.7 Static current of the super inverter                                  | . 73 |

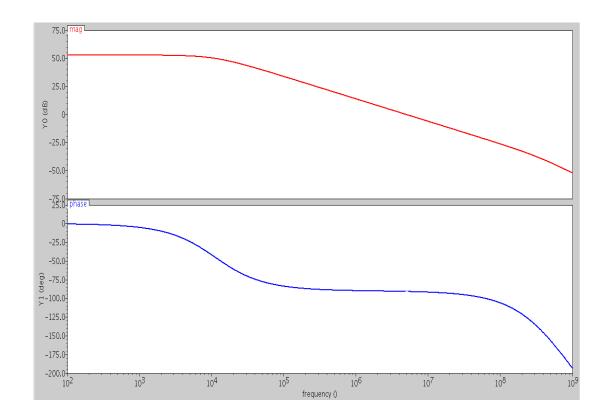

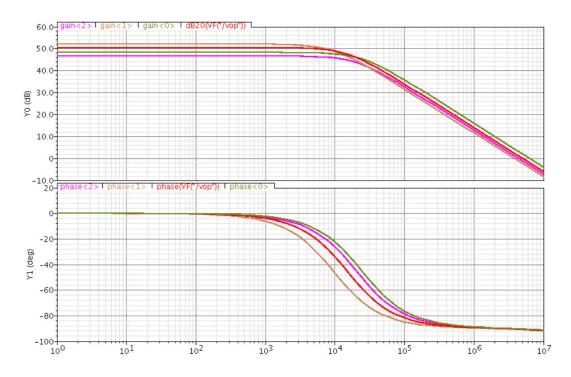

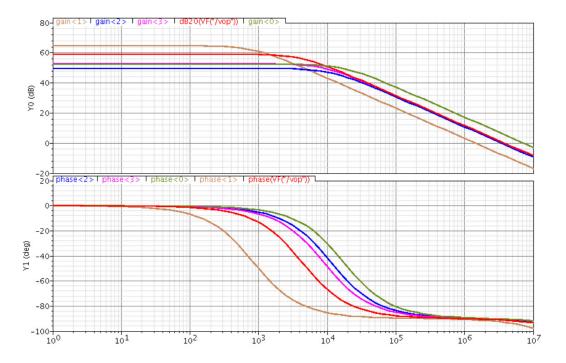

| Figure 5.8 AC response of the super inverter                               | 74 |

|----------------------------------------------------------------------------|----|

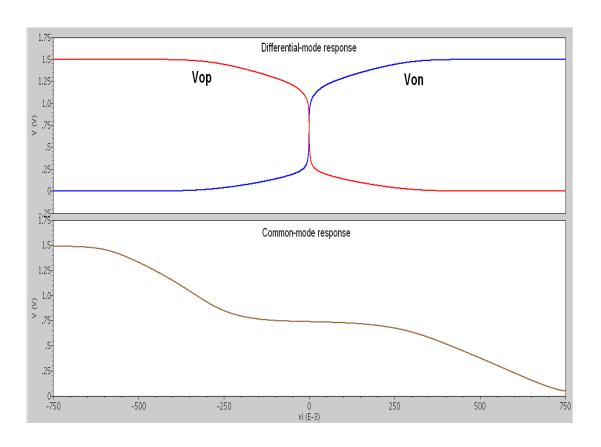

| Figure 5.9 Differential-mode DC response of the super inverter             | 75 |

| Figure 5.10 Common-mode DC response of the super inverter                  | 75 |

| Figure 5.11 DC current variations of the super inverter                    | 76 |

| Figure 5.12 AC responses of the super inverter (excluding the "blue" case) | 76 |

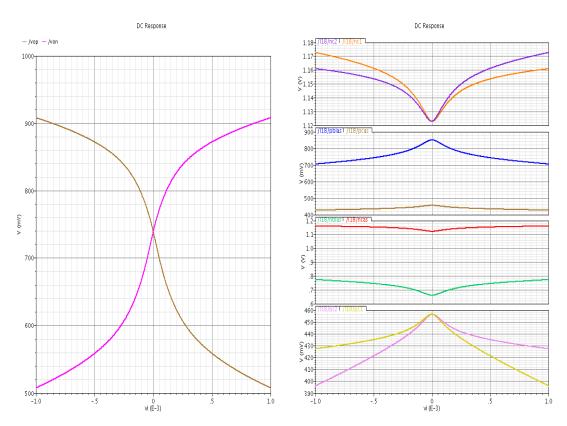

| Figure 5.13 Circuit diagram of the new inverter                            | 77 |

| Figure 5.14 Common-mode feedback circuit in the new inverter               | 78 |

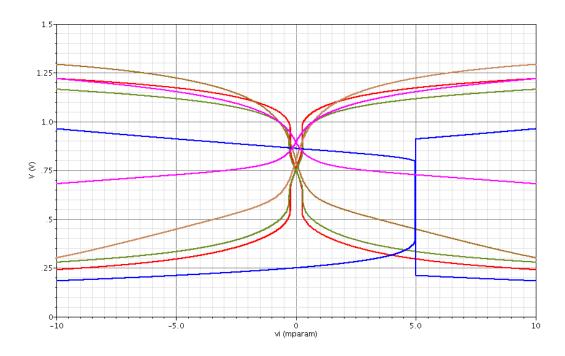

| Figure 5.15 DC transfer curve of the new inverter                          | 79 |

| Figure 5.16 Zoom-in view of the DC response                                | 80 |

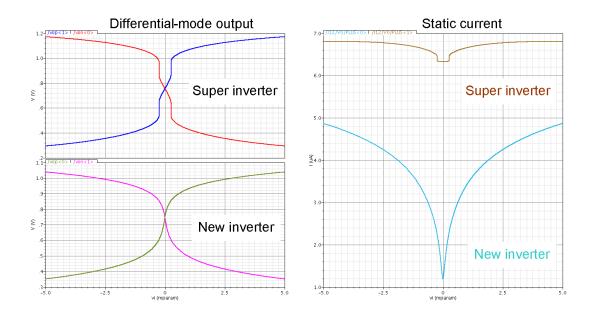

| Figure 5.17 Differential-mode DC comparisons                               | 81 |

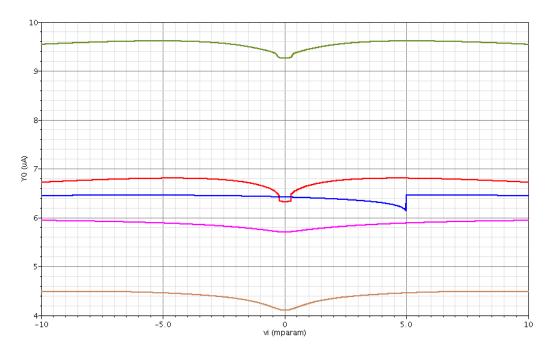

| Figure 5.18 Differential-mode DC responses of the new inverter             | 82 |

| Figure 5.19 Common-mode DC responses of the new inverter                   | 82 |

| Figure 5.20 DC current variations of the new inverter                      | 83 |

| Figure 5.21 AC responses of the new inverter.                              | 83 |

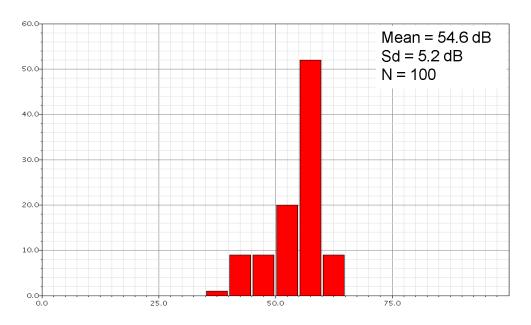

| Figure 5.22 Process variation on the A <sub>dm</sub> of the new inverter   | 84 |

| Figure 5.23 Mismatch analysis on the A <sub>dm</sub> of the new inverter   | 84 |

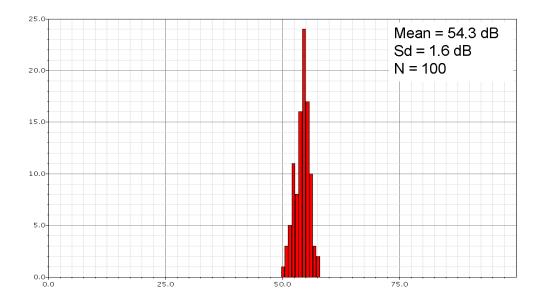

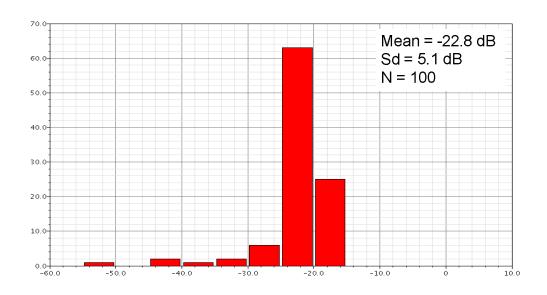

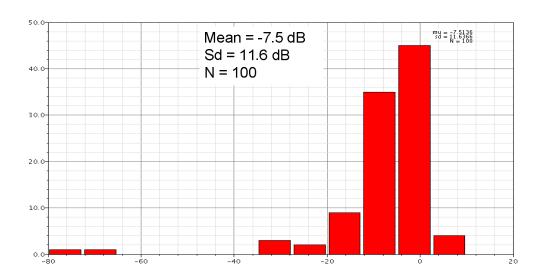

| Figure 5.24 Process variation on the A <sub>cm</sub> of the new inverter   | 85 |

| Figure 5.25 Mismatch analysis on the A <sub>cm</sub> of the new inverter   | 85 |

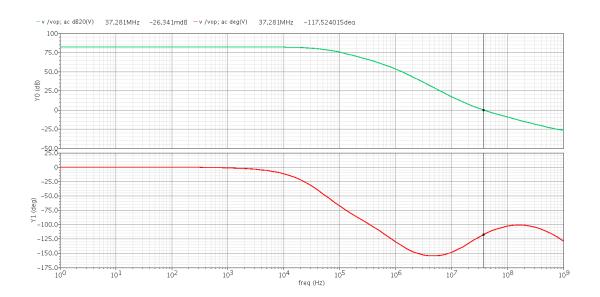

| Figure 5.26 Circuit diagram of the high-gain inverter amplifier            | 86 |

| Figure 5.27 DC response of the high-gain inverter amplifier                | 87 |

| Figure 5.28 AC response of the high-gain inverter amplifier                | 88 |

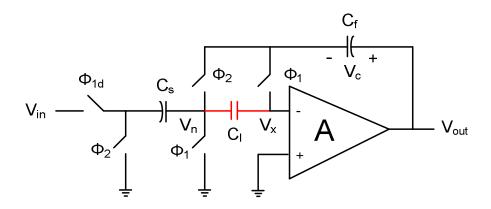

| Figure 5.29 Single-ended SC integrator with CDS                            | 89 |

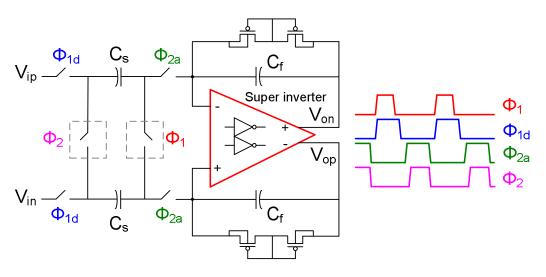

| Figure 5.30 Floating fully-differential SC integrator                                          |

|------------------------------------------------------------------------------------------------|

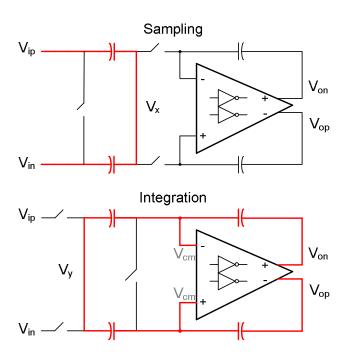

| Figure 5.31 Operation steps of the floating SC integrator                                      |

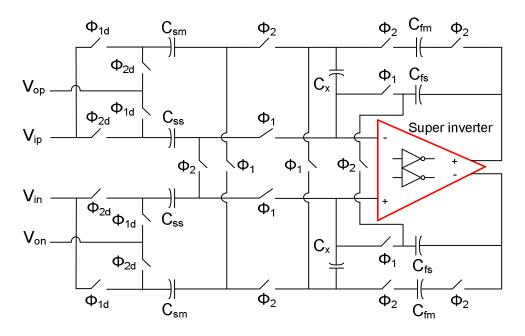

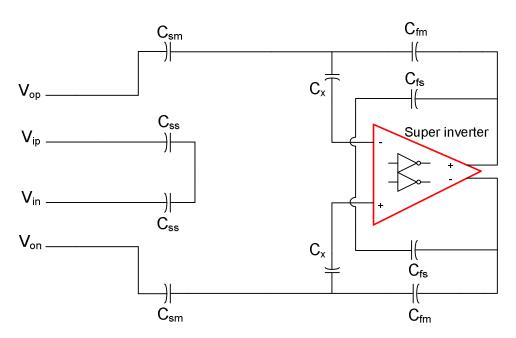

| Figure 5.32 SC integrator incorporating the floating CDS circuit                               |

| Figure 5.33 Two-path SC integrator in phase $\Phi_1$                                           |

| Figure 5.34 Two-path SC integrator in phase $\Phi_2$                                           |

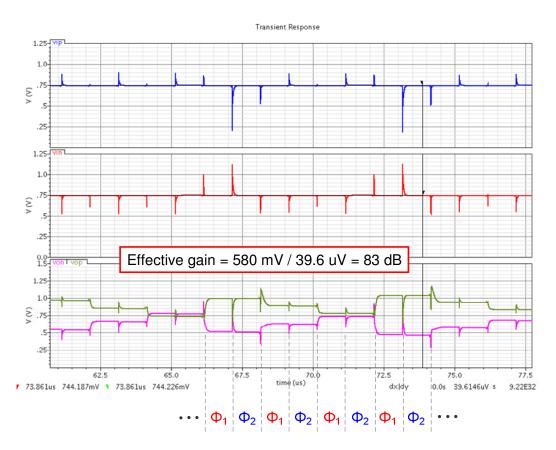

| Figure 5.35 Transient response of the two-path SC integrator                                   |

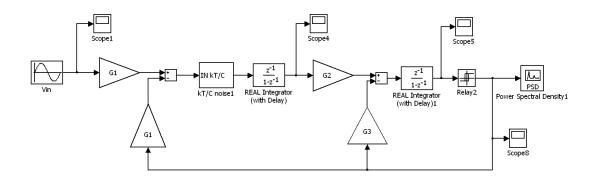

| Figure 6.1 Simulink model of the 2 <sup>nd</sup> -order modulator                              |

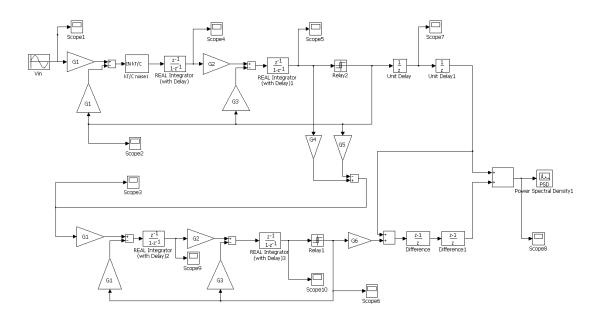

| Figure 6.2 Simulink model of the 4 <sup>th</sup> -order MASH                                   |

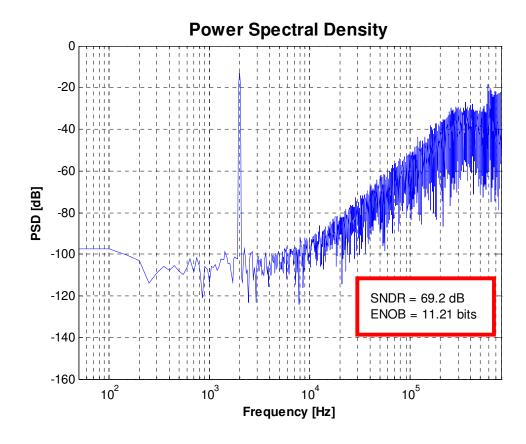

| Figure 6.3 Simulink spectrum of the 2 <sup>nd</sup> -order modulator                           |

| Figure 6.4 Simulink spectrum of the 4 <sup>th</sup> -order MASH                                |

| Figure 6.5 Circuit diagram of the prototyped 2 <sup>nd</sup> -order modulator                  |

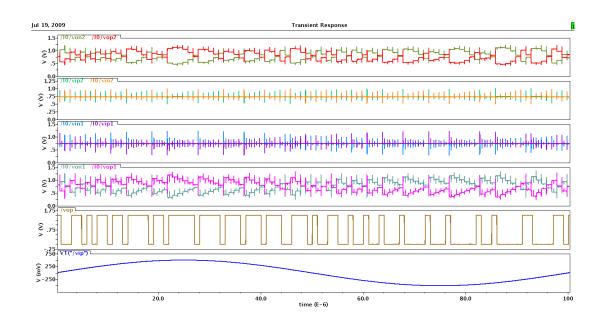

| Figure 6.6 Transient responses of the modulator                                                |

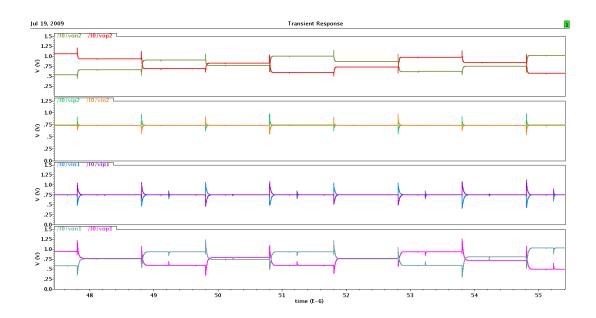

| Figure 6.7 Zoom-in view of the waveforms                                                       |

| Figure 6.8 Simulated output spectrum based on an 8192-point DFT 105                            |

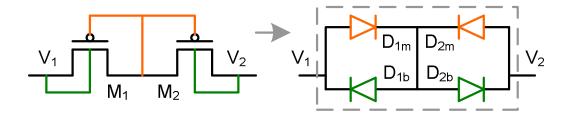

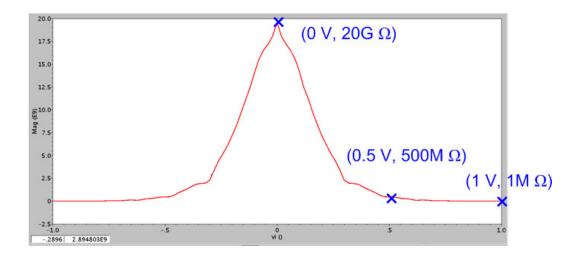

| Figure 6.9 Pseudo-resistor and its circuit representation                                      |

| Figure 6.10 Simulated resistance of the pseudo-resistor                                        |

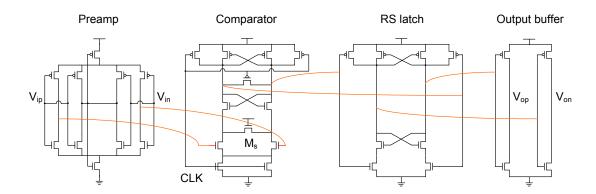

| Figure 6.11 Circuit diagram of the single-bit quantizer                                        |

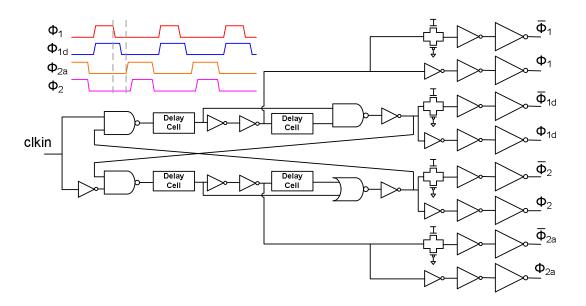

| Figure 6.12 Circuit diagram of the non-overlapping clock generator                             |

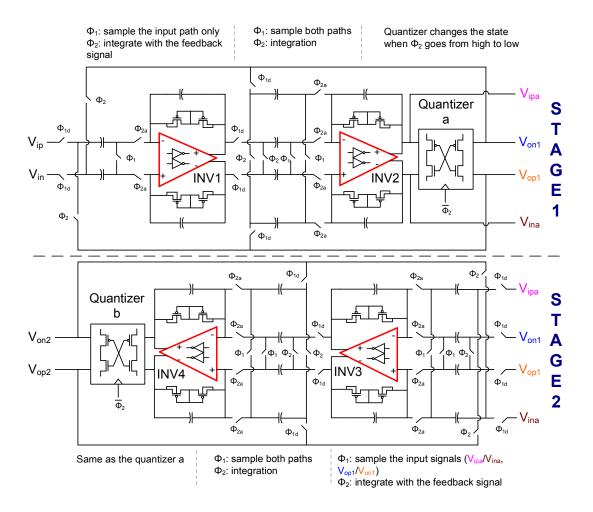

| Figure 6.13 Circuit diagram of the 4 <sup>th</sup> -order MASH architecture (no CDS) 109       |

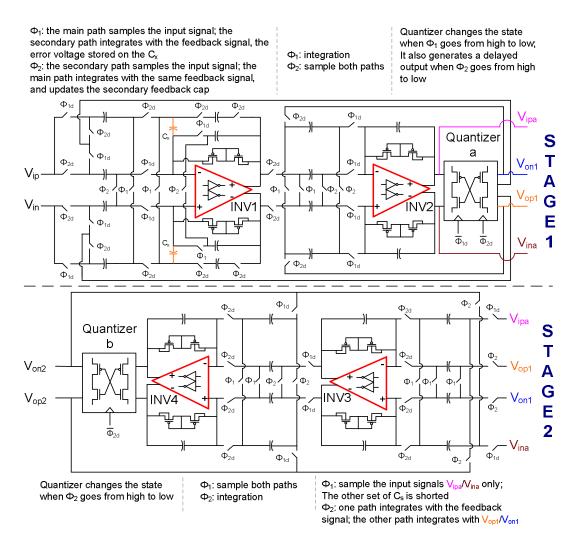

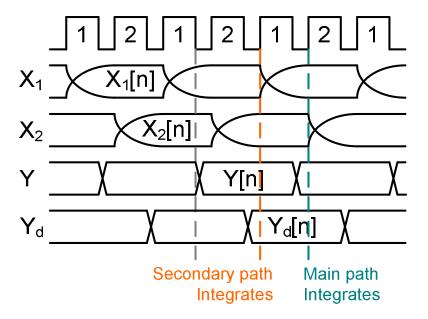

| Figure 6.14 Circuit diagram of the 4 <sup>th</sup> -order MASH architecture (CDS included) 110 |

| Figure 6.15 Timing diagram of the first modulator stage                                        |

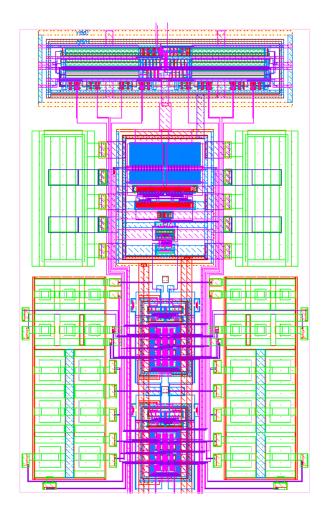

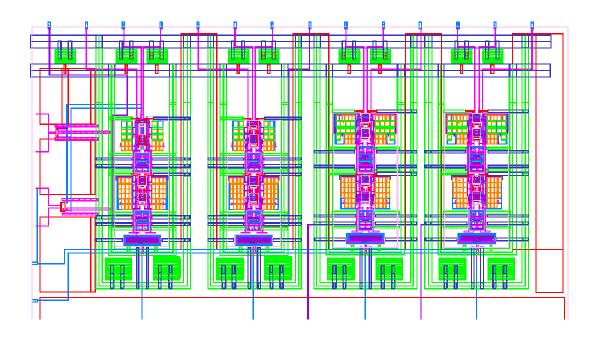

| Figure 6.16 Layout view of the 2 <sup>nd</sup> -order modulator (135 μm x 218 μm)              |

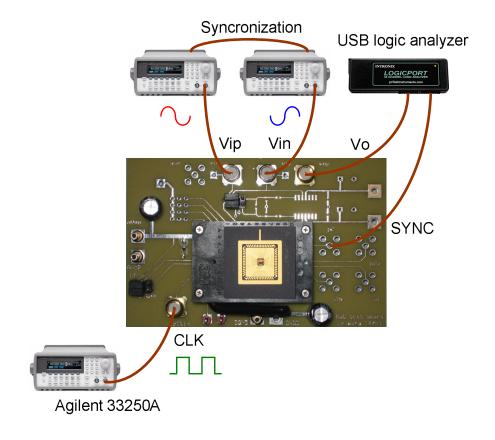

| Figure 7.1 Testing board and the equipment setup                                   | 116 |

|------------------------------------------------------------------------------------|-----|

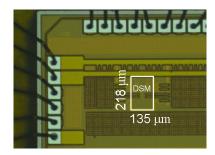

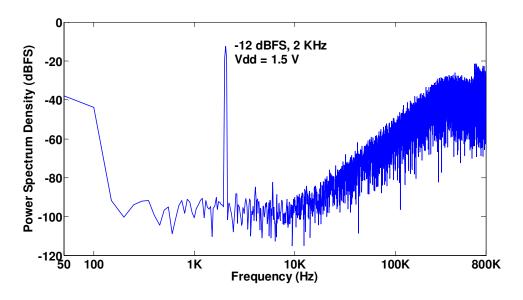

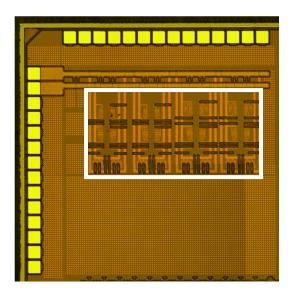

| Figure 7.2 Chip microphotograph of the 2 <sup>nd</sup> -order modulator            | 118 |

| Figure 7.3 Measured output spectrum of the 2 <sup>nd</sup> -order modulator        | 119 |

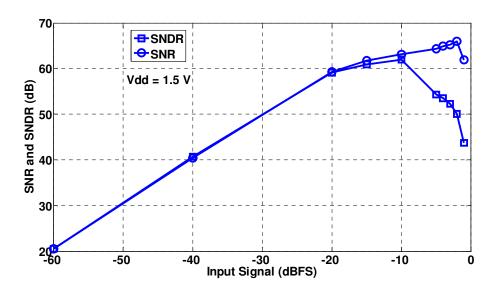

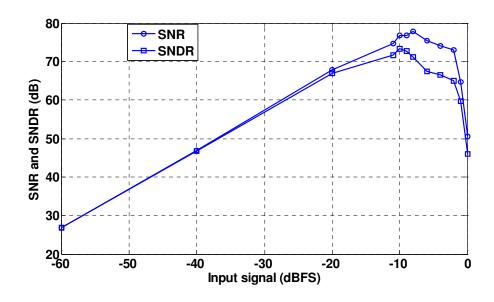

| Figure 7.4 Measured SNR/SNDR curve of the 2 <sup>nd</sup> -order modulator         | 119 |

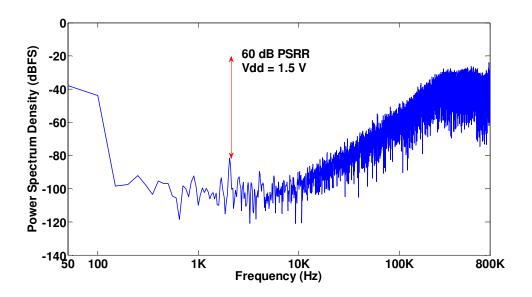

| Figure 7.5 Measured PSRR with -20 dBFS 2 KHz supply noise                          | 120 |

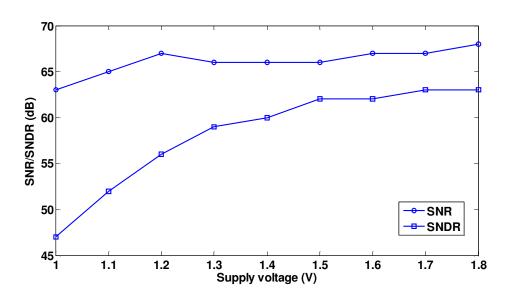

| Figure 7.6 Peak SNR and SNDR versus supply voltage                                 | 120 |

| Figure 7.7 Chip microphotograph of the MASH prototypes                             | 122 |

| Figure 7.8 Measured output spectrums of the prototype MASH1                        | 123 |

| Figure 7.9 Measured SNR/SNDR curve of the prototype MASH1                          | 124 |

| Figure 7.10 Measured output spectrums of the prototype MASH4                       | 125 |

| Figure 7.11 Measured SNR/SNDR curve of the prototype MASH4                         | 126 |

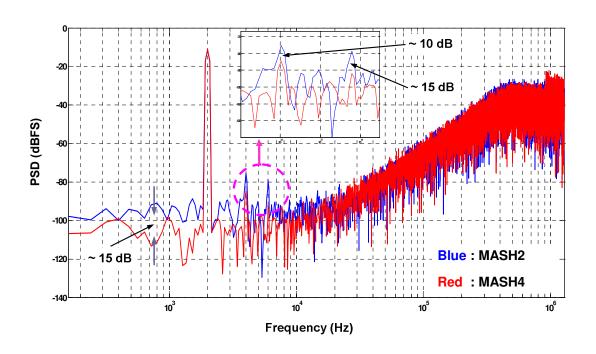

| Figure 7.12 Measured $2^{nd}$ -order output spectrums of MASH4 versus MASH2        | 127 |

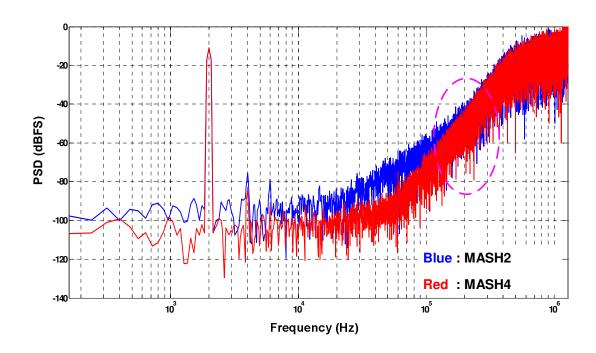

| Figure 7.13 Measured 4 <sup>th</sup> -order output spectrums of MASH4 versus MASH2 | 128 |

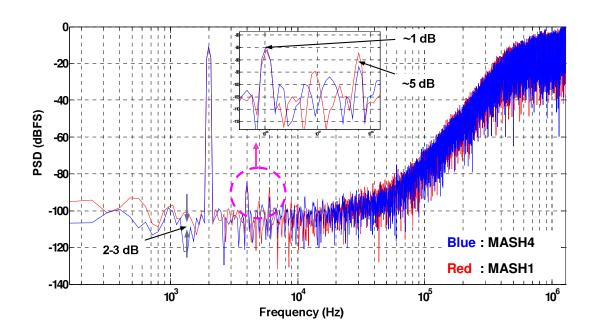

| Figure 7.14 Measured 4 <sup>th</sup> -order output spectrum of MASH4 versus MASH1  | 129 |

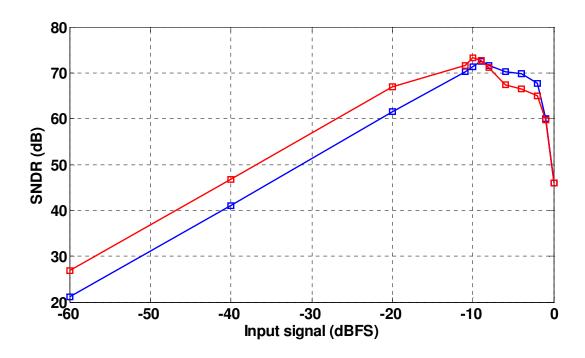

| Figure 7.15 Measured SNDR curve of MASH4 (blue) versus MASH1 (red)                 | 129 |

| Figure 7.16 State of the art in the ADC design                                     | 131 |

# LIST OF TABLES

| Table 3.1 Clock jitter versus clock skew                          | 2 |

|-------------------------------------------------------------------|---|

| Table 4.1 Delta-sigma ADC versus SAR ADC                          | 2 |

| Table 4.2 CT modulator versus DT modulator                        | 5 |

| Table 4.3 Single-loop versus MASH                                 | 7 |

| Table 4.4 Opamp versus Inverter amplifier                         | 2 |

| Table 5.1 Transistor sizing of the super inverter                 | 0 |

| Table 5.2 Performance summary of the super inverter               | 4 |

| Table 5.3 Performance summary of the new inverter                 | 1 |

| Table 5.4 Performance summary of the high-gain inverter amplifier | 8 |

| Table 6.1 2 <sup>nd</sup> -order modulator parameters             | 1 |

| Table 6.2 4 <sup>th</sup> -order MASH parameters                  | 2 |

| Table 6.3 Configurations of the 2-2 MASH prototypes               | 2 |

| Table 7.1 Measurement summary for the modulator                   | 1 |

| Table 7.2 Performance comparison                                  | 1 |

| Table 7.3 Measurement summary for MASH1                           | 4 |

| Table 7.4 Measurement summary for MASH4                           | 6 |

| Table 7.5 Performance of MASH4 versus MASH1                       | 0 |

### I. INTRODUCTION

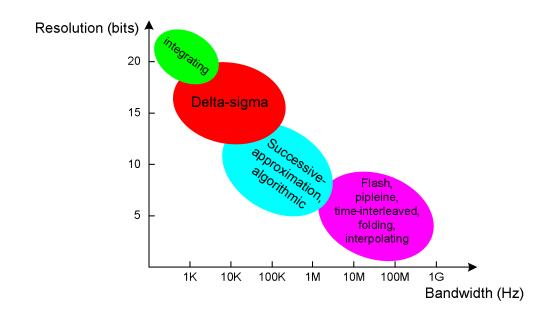

Delta-sigma analog-to-digital converters (ADC) have found widespread applications in high fidelity audio system, fractional-N frequency synthesizer, high precision image sensors, and many other electronic devices [Moon05, Perrott02, and Chae10]. In comparison to other ADC architectures, such as dual slope integrating ADC, flash ADC, pipeline ADC, and successive approximation (SAR) ADC, delta-sigma ADC requires no digital calibration in most implementations, and simple antialiasing filters may be used. In addition, the resolution of delta-sigma ADC can be adapted easily by adjusting the sampling frequency according to different applications and operation modes. Due to the inherent memory effect of delta-sigma modulators, however, there is no one-to-one correspondence between the analog input sample and digital output bit(s) as in other ADC architectures. Therefore, a delta-sigma ADC may be reused in an event-based manner rather than cycle-by-cycle time-interleaving in a multi-channel system.

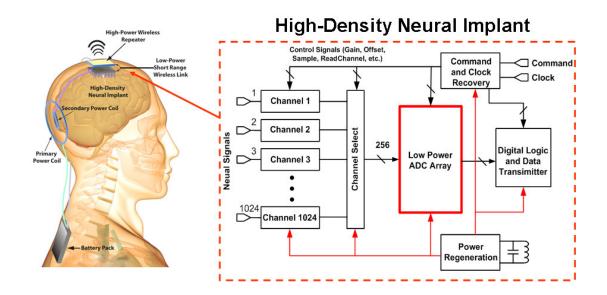

The delta-sigma ADC design will be used in a 1024 channel neural recording IC that includes a 16 x 16 array of these ADCs. Fig. 1.1 shows the system diagram of the high density neural implant (HDNI) currently under development at the Biomimetic group of UCSB. Due to the non-invasive requirement for the HDNI, inductive coupling will be utilized to transmit power from a nearby battery-powered power coil to an on-chip power coil, which is connected to the implant. In addition, the power consumption of the HDNI needs to be very low in order not to affect the neural cells in the ambient environment. Therefore, the total power budget for the HDNI, which

is allocated among pre-amplifiers, channel-select engine, ADC array, wireless transmitter, and digital circuits, should be less than 10 mW, and the power consumption of the ADC needs to be in the micro-watt range. Due to the high density nature of the implant, the ADC also needs to be very area efficient.

Figure 1.1: System diagram of the high density neural implant

### A. Motivation

Over the years, there has been extensive research conducted on the delta-sigma ADC to further improve its resolution, signal bandwidth, and power efficiency. To achieve higher resolution, the multi-stage noise shaping architecture (MASH) has been demonstrated [Matsuya87], which cascades two or more stages of first and/or second order single-loop delta-sigma modulators to achieve higher order noise

shaping through cancellation. Since the signal flow from the first stage to other stages is unidirectional, the overall stability margin in MASH architectures is of the lower order feedback systems. This topology usually requires high gain operational amplifiers (Opamp) to enhance the matching accuracy between the analog loop filter and digital cancellation logic, implying higher power consumption and system complexity. To enable the use of a low gain Opamp in MASH architectures, the sturdy-MASH architecture [Maghari09] feeds the second stage output back into the first stage at its output node to achieve the desired noise cancellation. By eliminating the digital cancellation logic, this approach mitigates the Opamp gain requirements. Since the signal flow between the upper and lower stages becomes bi-directional, however, stability may be an issue in the sturdy-MASH modulator. To extend the signal bandwidth, continuous time (CT) delta-sigma ADC can be employed to replace the switched-capacitor (SC) circuits, thus relaxing the settling requirement for the Opamp and enhancing the overall operation speed of the ADC [Vijay09]. But the fabrication resolution for on-chip resistors severely limits the coefficient accuracy of the loop filters, and additional tuning circuitry are usually required. In addition, the coefficient inaccuracy of CT delta-sigma ADC also prevents its use in the MASH architectures. To lower the power consumption of the ADC, switched-Opamp architecture was proposed [Steyaert94] to turn off the Opamp in the switchedcapacitor circuits during sampling phase and turn it on during integration phase. By eliminating the floating switches in the signal path, this approach allows low voltage operation and achieves high power efficiency for the ADC. However, the Opamp is

turned on and off periodically, and the settling time of the resulting transients limits the operation speed. To achieve both low voltage and high speed operation, various IC solutions, such as reset-Opamp [Bidari99], switched-RC [Ahn05], and switched-R-MOSFET-C [Kurahashi07], have been proposed. By avoiding the use of voltage boosting or bootstrapping techniques, these low voltage solutions are compatible with sub-micron CMOS processes and realizes low power consumption for the ADC. To further boost the power efficiency of the ADC, double sampling technique [Kim08] utilizes the Opamp during both sampling and integration phases by including an additional set of sampling capacitor and switches, which allows lower static current for the Opamp. But this arrangement also increases the input-referred KT/C noise and overall silicon overhead.

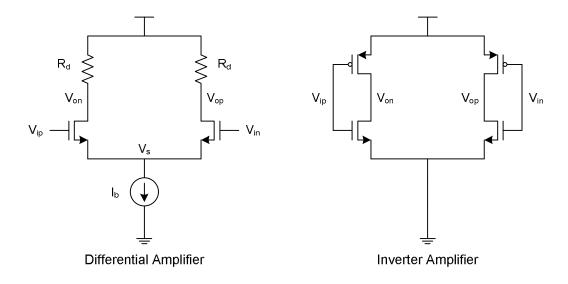

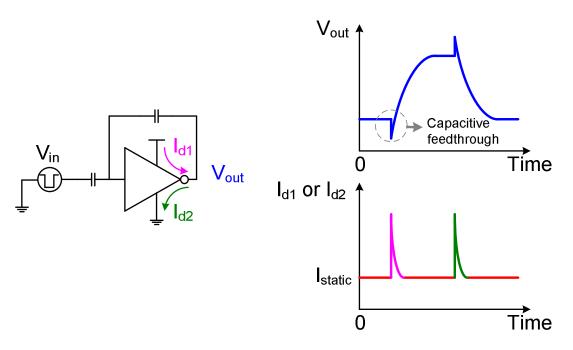

Aside from those techniques, we also noticed a recent research thrust in literature in developing inverter amplifiers-based SC circuits [Han09, Van08]. In an inverter-based design, the inverter serves as an active feedback element and its transition region is utilized for amplification. The simplicity and versatility of the inverter make this solution attractive and promising. In modern CMOS processes, however, the DC gain of conventional push-pull inverter amplifiers is merely 20-30 dB, rendering it incompetent for high-resolution analog applications. Furthermore, the single-ended nature of the inverter necessitates the use of pseudo-differential structures to increase the dynamic range and common-mode noise rejection, which complicates the overall system design.

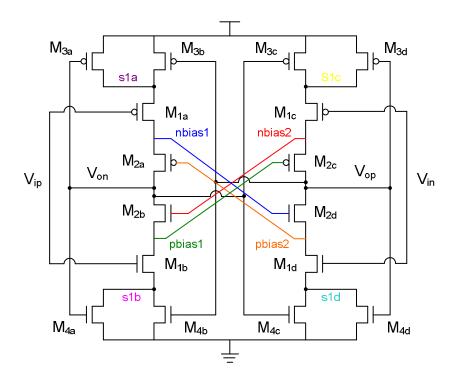

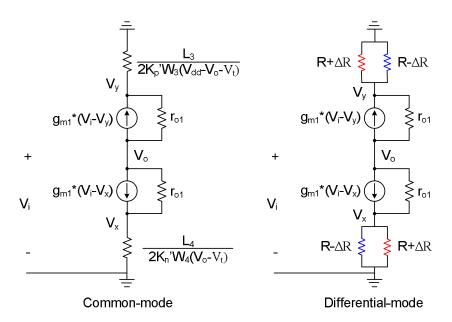

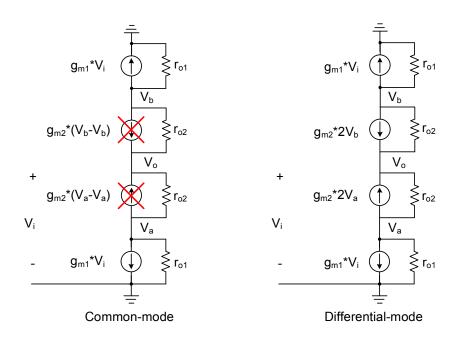

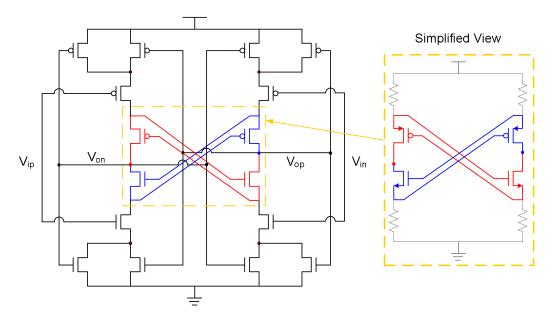

In this dissertation, a suite of novel self-biased inverter amplifiers are proposed: the super inverter, the new inverter, and the high-gain inverter. By responding to the differential-mode (DM) signal and common-mode (CM) noises in different ways, all the three inverter amplifiers achieve high DM gain, low CM gain, high supply noise rejection, and fully differential operation. Through employing the self-biasing technique, these inverter amplifiers also show high power efficiency, mismatch tolerance, small form factor, and scalability for different technology nodes. Due to the different operation principles of these inverter amplifiers, they also differ from each other in various aspects such as gain, bandwidth, static current, and linearity performances. Therefore, these inverter amplifiers can be optimally utilized in SC circuits for different applications and design requirements. All the three inverter amplifiers in the dissertation were designed by Prof. Theogarajan, while the modeling, sizing, layout, and chip testing were done by the author.

Furthermore, a floating correlated double sampling (CDS) scheme has been devised to improve the gain-linearity performance of the inverter amplifiers for the implementation of MASH architecture. The floating CDS technique greatly enhances the matching accuracy between the analog loop filter and digital cancellation logic, lowers the in-band noise floor, and suppresses both even and odd order harmonic distortions. Therefore, additional design freedom is attained for choosing between the high-gain inverter amplifier (high gain, high linearity, and high power consumption) without CDS and the low-power inverter amplifiers (low gain, low linearity, and low power consumption) with CDS. To demonstrate the design methodology, these

inverter amplifiers have been implemented in a prototype  $2^{nd}$ -order delta-sigma modulator and  $4^{th}$ -order MASH architectures fabricated in a 0.13  $\mu m$  CMOS process. Chip measurements show promising results, clearly demonstrating the efficiency and flexibility of the proposed inverter amplifier-based SC circuits for delta-sigma modulation.

# **B.** Organization

The dissertation is organized in the following manner: chapters II, III, IV review the relevant circuit and system-level considerations in the delta-sigma ADC design. Chapters V, VI, VII, and VIII present the inverter amplifier-based design methodology, implementation details, and measurement results. Chapter VIII concludes the whole dissertation.

Chapter II starts with the explanation of the first order delta-sigma modulator to gain an intuitive understanding, and then extends to higher order loop dynamics to reach a general conclusion. The design of the decimation filter, which is an indispensable part of all delta-sigma ADCs, will also be briefly reviewed.

Chapter III describes the circuit-level nonideal effects that affect the achievable performance of the delta-sigma ADC. These nonidealities need to be understood before new circuit topologies or system architectures can be innovated.

Chapter IV compares the system architectures of delta-sigma ADCs in various perspectives. From these comparisons, the advantages and disadvantages of each topology can be identified, and the modulator topology can be tailored for different applications and design targets.

Chapter V presents the self-biased inverter amplifier topologies and floating CDS technique. The operation principles of these inverter amplifiers will be investigated at both large-signal and small-signal levels. The pros and cons of each inverter amplifier will be discussed and compared, and the design guidelines will also be given. The second part of this chapter explains the floating CDS technique in detail.

Chapter VI demonstrates the additional implementation details of both the  $2^{nd}$  order delta-sigma modulator and  $4^{th}$  order MASH architectures at the system, circuit, and layout levels.

Chapter VII discusses the testing setup and measurement results.

Chapter VIII summarizes the contributions of the dissertation and provides future directions.

# II. OVERVIEW OF DELTA-SIGMA ADC

### A. Delta-Sigma Modulator

Basically, the delta-sigma modulator is a nonlinear feedback system, which forms a low-pass filter for the input signal and a high-pass filter for the quantization noise [Spang62]. The separation of signal and quantization noise in frequency domain enables the use of digital filters in the following to remove the high-pass filtered quantization noise, and therefore a high resolution ADC can be realized with a coarse quantizer. In most feedback systems, a high gain active element at the signal band is inserted into the loop, and the feedback tends to desensitize the nonidealities of the active element and achieve accurate signal processing. Hence, a relatively low performance amplifier can be employed to achieve high resolution data conversion in delta-sigma modulators, while the performance of the Opamps in other ADC architectures directly limits the achievable resolution due to the open-loop structures.

### 1. First order loop dynamics

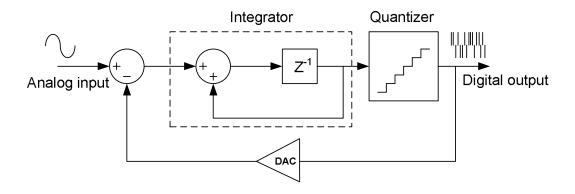

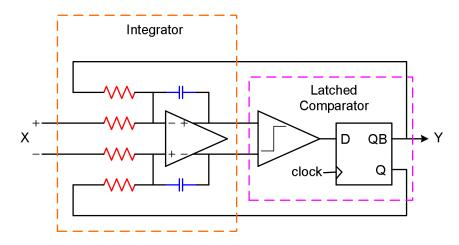

Fig. 2.1 shows the system diagram of the 1<sup>st</sup>-order discrete-time (DT) delta-sigma modulator. The sampled input is fed into an integrator, which is usually realized with a SC integrator in the DT implementations or an active-RC integrator in the CT implementations. For an ideal integrator, its DC gain is infinity since the output of the integrator under DC excitation keeps increasing and never reaches the steady-state. As the signal frequency increases, the gain of the integrator drops since the sampled

input is varying with time and the steady-state output has finite swing. Basically, the integrator is a high gain active element at baseband and it can serve as the loop filter in delta-sigma modulators. The output of the integrator feeds into a low resolution quantizer, usually single-bit in many implementations, to generate the digital outputs. The digital output contains both the signal and the quantization noise, which will be fed back to the modulator input for the next integration. Intuitively, the delta-sigma modulator behaves like a unity-gain amplifier for the input signal, and the digital output follows the analog input in both amplitude and frequency. On the other hand, the high gain active element is located in the feedback path for the quantization noise transfer function, so the noise transfer function of the delta-sigma modulator becomes a high-pass filter.

Figure 2.1: System diagram of the 1<sup>st</sup> order delta-sigma modulator

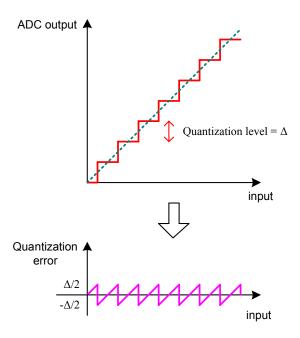

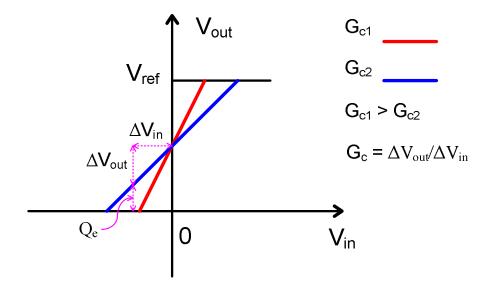

To gain more insight, the 1<sup>st</sup> order loop dynamics also needs to be analyzed in a quantitative manner. Firstly, the quantization noise needs to be expressed in a mathematical form. Fig. 2.2 shows a typical ADC transfer curve and the quantization

error under linear excitation. The cyan curve is an ideal ADC transfer curve with infinite resolution. The red curve is an actual ADC transfer curve with finite resolution. The step in the red curve represents the quantization level  $\Delta$  of the ADC, and the difference between the two curves gives the quantization noise or error, represented by a sawtooth waveform swinging between  $\Delta/2$  and  $-\Delta/2$ . Assuming the input signal is busy, the quantization error  $Q_e$  can be treated as a random variable with constant probability density between  $\Delta/2$  and  $-\Delta/2$ . Therefore, the power of the quantization error  $Q_e^2$  can be calculated as follows. In Eq. 2.2,  $V_{ref}$  and N refer to the reference voltage and bits of resolution of the quantizer, respectively.

$$Q_e^2 = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} x^2 dx = \frac{\Delta^2}{12}$$

(2.1)

$$\Delta = \frac{V_{ref}}{2^N} \tag{2.2}$$

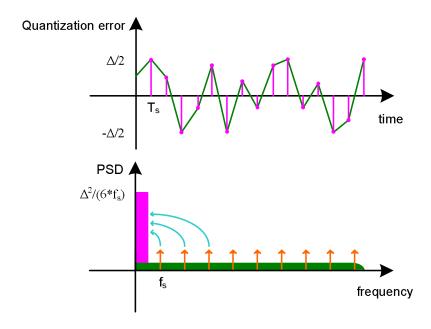

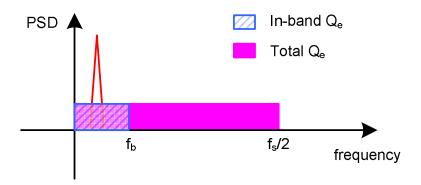

Fig. 2.3 shows a fictitious continuous waveform of the quantization noise by drawing a straight line between each pair of successive points on the discrete waveform of the quantization noise. Obviously, the power of this continuous waveform is  $\Delta^2/12$  and its bandwidth is much wider than the sampling frequency  $f_s$  of the quantizer. Since the quantizer is basically a sampled data system, the actual quantization noise waveform is a sampled version of this continuous waveform. Due to noise folding, the high frequency noise power will be aliased down to the baseband, and the total in-band power of the quantization noise is  $\Delta^2/12$  with a flat power spectral density (PSD) from DC to  $f_s/2$  [Bennett48].

Figure 2.2: ADC transfer curve and the quantization error

Figure 2.3: Quantization noise waveform and in-band power spectral density

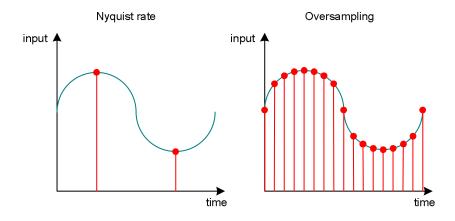

It is well-known that the in-band quantization noise is reduced if the input signal is sampled at a higher frequency than the Nyquist rate  $f_n$ . Fig. 2.4 shows the comparison between the Nyquist rate sampling and oversampling. The reason why oversampling reduces the in-band quantization noise is due to a more profound physics behind many phenomena: the averaging effect [Papoulis04]. For example, the flicker noise of a Metal-Oxide-Semiconductor (MOS) device can be reduced by proportionally increasing its W and L, and the larger area tends to smooth the surface states of the channel. For a full-scale sinusoidal input, the maximum signal to quantization noise ratio (SNR) of an oversampling ADC is given by:

$$Q_e^2 = \frac{\Delta^2}{12 \times QSR} \tag{2.3}$$

$$SNR_{\text{max}} = 6.02 \times N + 1.76 + 10 \times \log_{10}(OSR)$$

(2.4)

In Eq. 2.3, OSR is the ratio of the sampling frequency to the nominal Nyquist rate. It can be seen that the SNR of an oversampling ADC increases by 3 dB or 0.5 bit for every doubling of the sampling frequency, as illustrated in Fig. 2.5.

Figure 2.4: Nyquist rate sampling versus oversampling

Figure 2.5: Power spectral density of an oversampling ADC

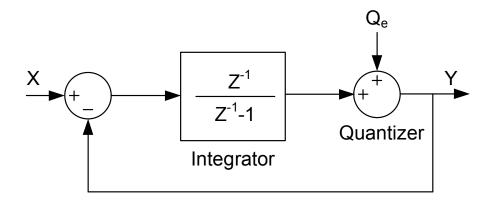

For a coarse quantizer, however, the required sampling frequency would be unrealistically high to achieve reasonable resolution. By high-pass filtering the quantization noise using a delta-sigma modulator, the requirement on the sampling frequency can be greatly reduced. Fig. 2.6 shows the simplified model of the 1<sup>st</sup>-order delta-sigma modulator. From this model, its signal transfer function STF and noise transfer function NTF can be found, given by:

$$STF(Z) = \frac{Y}{X} = Z^{-1}$$

(2.5)

$$NTF(Z) = \frac{Y}{Q_e} = 1 - Z^{-1}$$

(2.6)

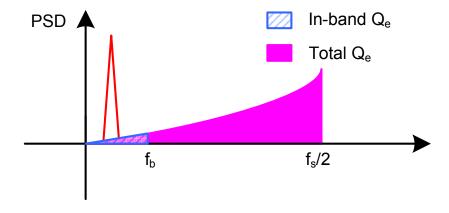

In the Z-domain, the STF is a clock cycle delay, and the NTF is a differentiator. To find the in-band quantization noise of the 1<sup>st</sup>-order modulator, the power of the noise transfer function |NTF(Z)|<sup>2</sup> will be integrated from DC to the Nyquist frequency [Johns97]. Then, the maximum SNR under both oversampling and 1<sup>st</sup>-order noise shaping can be estimated, as shown in Eq. 2.7 and 2.8. It is seen that the maximum

SNR of the 1<sup>st</sup>-order modulator increases by 9 dB or 1.5 bits for every doubling of the sampling frequency, as illustrated in Fig. 2.7.

$$Q_e^2 = \frac{\Delta^2 \pi^2}{36 \times OSR^3} \tag{2.7}$$

$$SNR_{\text{max}} = 6.02 \times N + 1.76 - 5.17 + 30 \times \log_{10}(OSR)$$

(2.8)

Figure 2.6: Simplified model of the 1<sup>st</sup>-order delta-sigma modulator

Figure 2.7: Power spectral density of the 1<sup>st</sup>-order delta-sigma modulator

# 2. Higher order loop dynamics

To achieve more noise shaping, higher order delta-sigma modulator can be built. Basically, a higher order loop filter tends to have sharper transition from its pass band to stop band than a lower order filter, and more quantization noise can be moved to high frequency band. In the higher order modulator, more integrators are cascaded in a loop, and the number of the integrators determines the order of the system since each integrator contributes a DC pole.

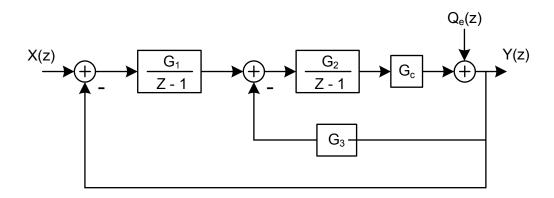

Fig. 2.8 shows a simplified model of the 2<sup>nd</sup>-order DT delta-sigma modulator [Boser88]. The attenuation factor G<sub>1</sub> is added to limit the voltage swing at the input of the first integrator since the feedback takes two clocks cycles. Without the attenuation, the integrator output will saturate even for a small input, and the effective gain of the amplifier in the integrator will drop, degrading the performance of the loop filter. More about the finite gain effect will be discussed in the next chapter. G<sub>2</sub> and G<sub>3</sub> are chosen to attain the desired STF and NFT. G<sub>c</sub> represents the effective gain of the quantizer, as illustrated in Fig. 2.9. For a single-bit quantizer, its gain is not well defined and dependent on the average input amplitude of the quantizer. Since the output of the modulator follows the input through the feedback,  $G_c$  must satisfy that  $G_1G_2G_c=1$ , statistically [Baker08]. For a single-loop delta-sigma modulator, G<sub>c</sub> is embedded in the loop transmission so it is not important. For a MASH modulator, however, G<sub>c</sub> is critical for precisely extracting the quantization noise. Otherwise, the accuracy of the noise cancellation would drop greatly. Eq. 2.9 and 3.0 show the STF and NTF of the 2<sup>nd</sup>-order delta-sigma modulator. Given that

$G_1G_2G_c$ =1 and  $G_{1,2,3}$  are chosen properly, the STF and NTF can simplified as shown in Eq. 3.1 and 3.2.

Figure 2.8: Simplified model of the 2<sup>nd</sup>-order delta-sigma modulator

Figure 2.9: Transfer curve of a single-bit quantizer

$$STF = \frac{G_1 G_2 G_c}{(Z-1)^2 + G_2 G_3 G_c (Z-1) + G_1 G_2 G_c}$$

(2.9)

$$NTF = \frac{(Z-1)^2}{(Z-1)^2 + G_2G_3G_c(Z-1) + G_1G_2G_c}$$

(2.10)

$$STF = Z^{-2}$$

(2.11)

$$NTF = (1 - Z^{-1})^2 (2.12)$$

It's clear that the STF is a two clock cycle delay and the NTF is a 2<sup>nd</sup>-order high-pass filter. Using the same method, the in-band quantization noise and maxim SNR of the 2<sup>nd</sup>-order delta-sigma modulator can be derived as given in Eq. 2.13 and 2.14. For the 2<sup>nd</sup>-order modulator, the PSD of the shaped quantization noise increases at a rate of 40 dB per decade, while it is 20 dB per decade for the 1<sup>st</sup>-order modulator. In addition, the maximum SNR increases by 15 dB or 2.5 bits for every doubling of the sampling frequency.

$$Q_e^2 = \frac{\Delta^2 \pi^4}{60 \times QSR^5}$$

(2.13)

$$SNR_{\text{max}} = 6.02 \times N + 1.76 - 12.19 + 50 \times \log_{10}(OSR)$$

(2.14)

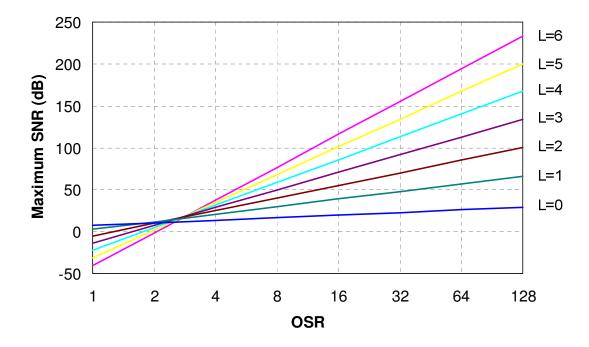

The in-band quantization noise and maximum SNR can be generalized for any L<sup>th</sup>-order delta-sigma modulators, given by Eq. 2.15 and 2.16. In general, the maximum SNR of the L<sup>th</sup>-order modulator increases by 3(2L+1) dB or (L+0.5) bits for every doubling of the sampling frequency, as shown in Fig. 2.10. In reality, there are many circuit nonidealities, such as KT/C noise, greatly limiting the achievable resolution. Furthermore, L<4 usually needs to be satisfied in a single-loop delta-sigma modulator for the stability consideration. To achieve higher order (L>=4) noise shaping, MASH

architectures will be exploited instead. Some advanced topics of delta-sigma ADCs will be investigated in the following chapters, and the core of the dissertation is also unveiled.

$$Q_e^2 = \frac{\Delta^2}{12} \cdot \frac{\pi^{2L}}{(2L+1) \times OSR^{2L+1}}$$

(2.13)

$$SNR_{\text{max}} = 6.02N + 1.76 - 10\log_{10}(\frac{\pi^{2L}}{2L+1}) + (2L+1) \times 10\log_{10}(OSR)$$

(2.14)

Figure 2.10: Maximum SNR versus OSR

#### **B.** Decimation Filter

At the output of the delta-sigma modulator, analog input signal has been converted into low-resolution digital outputs. Although the quantization noise is moved to high frequency, it is still in the output bits. Hence, the other part of the delta-sigma ADC design is to build the digital decimation filter, which filters out the high frequency quantization noise and converts the coarse binary bits into high resolution digital outputs. In this section, the design of the decimation filter will be briefly reviewed, completing the introduction of the delta-sigma ADC.

Intuitively, the decimation filter calculates the running averages of the incoming digital bits from the delta sigma modulator. After the decimation filter, the low frequency components are retained, but the high frequency quantization noise has been removed. The digital outputs are also down-sampled to the Nyquist rate for further signal processing.

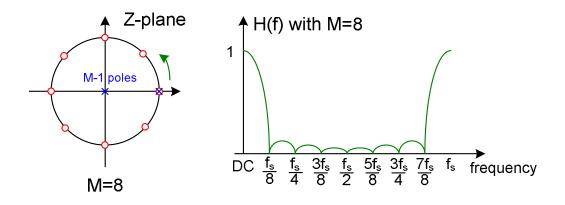

Eq. 2.15 shows the transfer function of a typical running-average filter, with a decimation ratio of M. The pole and zero locations for M=8 are plotted in the Z-plane, and the frequency response can be found by moving around the unity circle, as shown in Fig. 2.11. Clearly, it has the low-pass filtering characteristics. Since the frequency response looks like a comb from DC to the sampling frequency, it's also known as the comb filter.

$$H(Z) = \frac{(1+Z^{-1}+Z^{-2}+\dots+Z^{-(M-1)})}{M} = \frac{1}{M} \cdot \left(\frac{1-Z^{-M}}{1-Z^{-1}}\right)$$

(2.15)

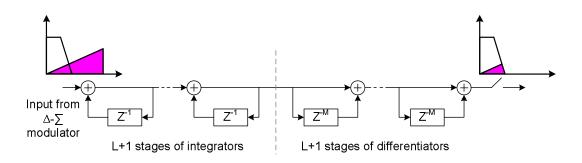

In the decimation filter, multiple running-average filters are cascaded and organized in a power-efficient form, as illustrated in Fig. 2.12. The cascade stages usually need to be higher than the order of the preceding modulator to achieve sufficient out of band rejection [Candy86].

Figure 2.11: Running-average filter with M=8

Figure 2.12: Part of the Decimation filter –  $Sinc^{L+1}FIR$  filter

## III. CIRCUIT CONSIDERATIONS

In this chapter, common circuit nonidealities that limit the achievable performance of the delta-sigma ADC will be discussed in different perspectives: Opamp nonidealities, noise, and distortion. Those issues are critical in understanding the different system architectures of the delta-sigma ADC, so this chapter precedes the system discussions. In many high-speed applications, the quantizer nonidealities, such as comparator hysteresis, metastability, and delay, also affect the resulting SNR. Due to the low frequency operation of this design, the discussion of those issues will be omitted for simplicity.

# A. Opamp Nonidealities

In both DT and CT delta-sigma modulators, Opamp serves as the active feedback elements in the loop filter. It affects the performance of the delta-sigma modulator in many aspects: integrator leakage, flicker noise and DC offset, harmonic distortion, and matching accuracy of the loop filters. Furthermore, it also dominates the power consumption of the modulator due to the static current.

### 1. Finite gain effect

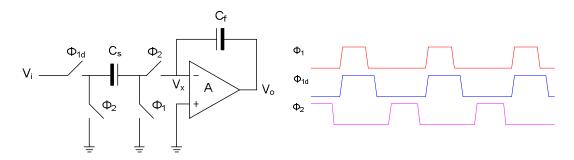

Due to the limited transconductance (g<sub>m</sub>) and output resistance (r<sub>o</sub>), any Opamp has finite DC gain ranging from 20 dB to 100 dB, which causes degradations in the low frequency noise shaping and matching accuracy of the loop filters. Fig. 3.1 shows a single-ended SC integrator and the associated timing diagram of the clock signals.

During the integration phase, the potential at the virtual ground,  $V_x$ , is initially pushed down to  $-V_i[n]$  due to the feedthrough effect of  $C_s$ , then the negative feedback around the Opamp asymptotically pulls  $V_x$  back to ground potential. For an ideal Opamp with infinite gain, the steady-state value of  $V_x$  is zero, and all the charges on  $C_s$  will be completely transferred to  $C_f$ . For a practical Opamp with finite gain of  $A_s$ ,  $V_x$  would settle at  $-V_o[n+1]/A$  instead, and a fraction of the charges on  $C_s$  leak away. The integrator leakage effect moves the pole of the integrator away from DC, thus levels off the shaped quantization noise in the baseband.

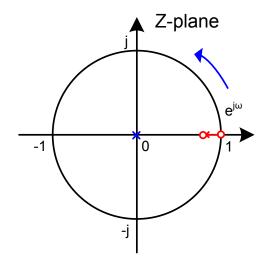

Figure 3.1: A delaying switched-capacitor integrator

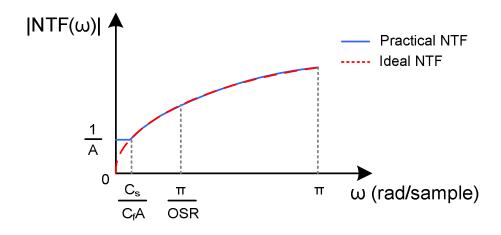

To quantify the leakage effect, the integrator transfer function with finite Opamp gain of A can be found by applying the charge conservation for both sampling and integration clock phases. As shown in Eq. 3.1 and 3.2, the pole of the integrator moves away from DC (Z=1) to Z=1-(C<sub>b</sub>/C<sub>f</sub>)/A inside the unity circle. The DC gain of the integrator also becomes A, instead of infinity. Eq. 3.3 gives the first order NTF considering the integrator leakage effect, and Fig. 3.2 shows the Z-plane root locus of the NTF. The -3dB corner frequency of the NTF can be found by applying bilinear transform [Johns97], which is given in Eq. 3.4. Fig. 3.3 compares the frequency

responses between an ideal NTF and a practical NTF considering the integrator leakage.

In order to mitigate the resulting noise notch, it is necessary to keep the corner frequency within the signal bandwidth, as shown in Eq. 3.5. As a sanity check, A=OSR gives 0.2 dB additional noise, thus the integrator leakage effect is rarely serious. In most delta-sigma ADCs, the nominal OSR ranges from 64 to 256, thus the required Opamp gain needs to be around 40-50 dB. This can be easily achieved given today's amplifier design techniques, and the Opamp can be optimized for higher power efficiency or other performance targets. In general, it's acceptable to have an Opamp of A=OSR in the delta-sigma modulator design.

$$C_{s}V_{i}[n] + C_{f}V_{o}[n] \frac{1+A}{A} = C_{s}V_{o}[n+1]/A + C_{f}V_{o}[n+1] \frac{1+A}{A}$$

(3.1)

$$\frac{V_o(Z)}{V_i(Z)} = \frac{C_s}{C_f} \frac{1}{Z \left[ 1 + \left( 1 + \frac{C_s}{C_f} \right) \cdot \frac{1}{A} \right] - \left( 1 + \frac{1}{A} \right)} = A @ DC$$

(3.2)

$$NTF(f) \approx 1 - (1 - \frac{C_s}{C_f} \cdot \frac{1}{A})Z^{-1}$$

(3.3)

$$\omega_{-3dB} \approx \frac{C_s}{C_f A}$$

rad/sample (3.4)

$$\frac{C_s}{C_f A} < \frac{\pi}{OSR} \Rightarrow A > \frac{C_s}{C_f} \frac{OSR}{\pi} \Rightarrow A = \frac{1}{OSR}$$

(3.5)

Figure 3.2: Root locus of the 1st order NTF

Figure 3.3: Frequency response of the 1st order NTF

In the MASH architectures, however, much higher Opamp gain is often required to enhance the matching accuracy between the analog and digital signal paths. Finite Opamp gain changes the pole locations of the NTF and modifies the absolute gain factor of the integrator. The transfer function of a SC integrator with finite Opamp gain of A is rewritten in Eq. 3.6, 3.7 and 3.8, where a and D represent the nominal value and relative error of the integrator gain  $(C_s/C_f)$ , respectively.

$$H(Z) = \frac{V_o(Z)}{V_i(Z)} = \frac{a}{Z - p}$$

(3.6)

$$a' \approx a [1 - D - (1 + a)/A]$$

(3.7)

$$p \approx 1 - \frac{a}{A} \tag{3.8}$$

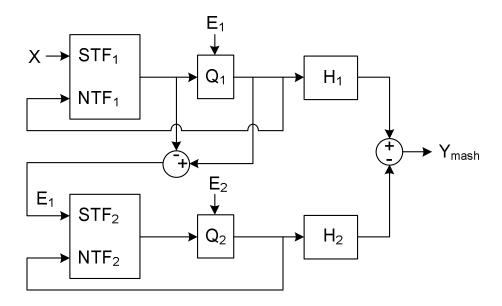

Fig. 3.4 shows a typical two-stage MASH architecture, where  $E_1$  is cancelled through the matching between NTF<sub>1</sub>H<sub>1</sub> and STF<sub>2</sub>H<sub>2</sub>. H<sub>1</sub> and H<sub>2</sub> are built with digital filters, and thus have ideal transfer functions. NTF<sub>1</sub> and STF<sub>2</sub> are analog filters, which will be affected by circuit nonidealities. To quantify the first order noise leakage, two assumptions are made: 1. STF<sub>2</sub> is an ideal function; 2. NTF≈1/H(Z) [Schreier04]. Eq. 3.9 clearly shows that there will be an unfiltered component approximately equal to  $E_1$ /A, and a first-order-shaped component dominated by the capacitor mismatching.

$$|H_{1l}(Z)| = |NTF_1H_1 - STF_2H_2|$$

$$= |NTF_1 - H_2|$$

$$= \left|\frac{Z - 1}{a} - \frac{Z - p}{a}\right|$$

$$\approx \left|\frac{1}{A} + (Z - 1) \cdot \left[D/a + (1 + 1/a)/A\right]\right|$$

(3.9)

Figure 3.4: Two-stage MASH architecture

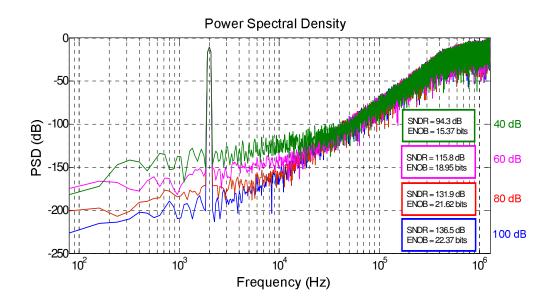

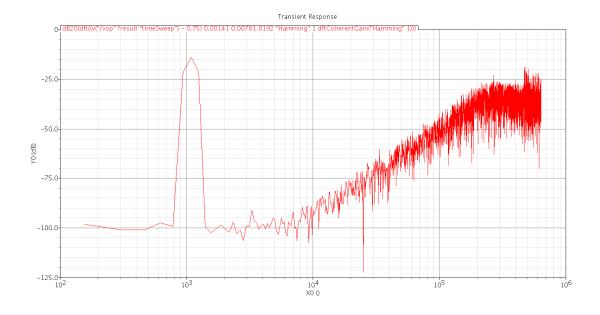

To analyze higher order noise leakage, matlab simulation can be utilized. Fig. 3.5 plots the simulated power spectral density (PSD) of a 2-2 MASH architecture assuming Opamp gain of 40, 60, 80, and 100 dB. Only quantization noise is simulated in the simulation, and other noise sources are turned off for clarity. In the overlaid output spectrums, it can be seen that there are an unfiltered leakage component roughly proportional to 1/A, and a second-order-shaped leakage component. Clearly, the mismatch between the filters warps up the in-band noise floor. On the other hand, the high frequency noise spectrum is still dominated by the  $4^{th}$ -order shaped quantization noise  $E_2$ . The corner frequency is determined by where the leakage noise spectrum of  $E_1$  meets the shaped noise spectrum of  $E_2$ . Intuitively, higher Opamp gain results in lower corner frequency, and hence better SNR possibility.

Figure 3.5: Opamp gain effects on the 4<sup>th</sup> order MASH

# 2. Settling time

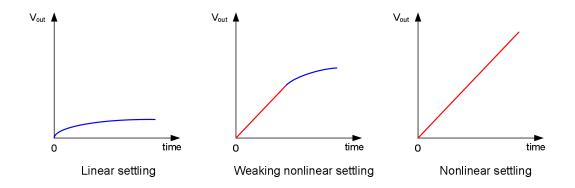

The previous section analyzes the steady-state behavior of the Opamp in the SC integrator, assuming infinite settling speed. During the transient time, any Opamp has finite settling speed due to the limited current available for charging or discharging the loading capacitors. In addition, the settling process of the OPAMP may be linear or nonlinear depending on the input amplitude.

For a small-signal input, the output current of the OPAMP is proportional to the input voltage, and the time constant of the feedback system keeps the same. For a given settling time, the steady-state output voltage will be proportional to the input voltage, corresponding to the linear settling region. For a large-signal input, the output current is limited by the maximally available current in the circuit, and in the given time the stead-state output voltage reaches a constant value, independent of the

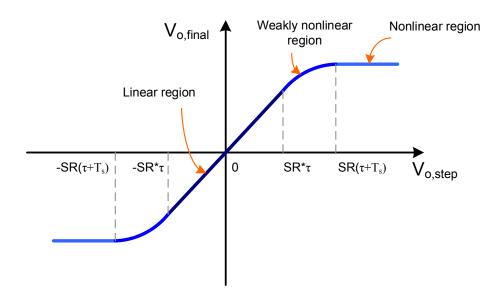

input voltage. This corresponds to the nonlinear settling or the slew-rate limiting region. Between these two regions, the output voltage first changes in a slew-rate limiting manner, then the OPAMP enters the small-signal operating mode, and the linear settling takes place for the rest of the period. This corresponds to the weakly nonlinear region. Fig. 3.6 illustrates the three cases of the settling process for different input amplitudes.

Figure 3.6: Three settling processes for different input steps

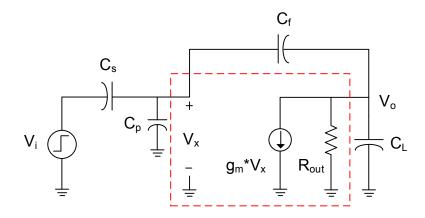

During the design phase, it is useful to quantify the time constant for the linear settling. Fig. 3.7 shows the small-signal circuit diagram of a single-ended SC integrator in the integration phase. By applying KCL and KVL, the Laplace-domain transfer function of the feedback system is shown in Eq. 3.10 and 3.11, assuming single-pole rolloff and infinite R<sub>out</sub> for the amplifier.

$$\frac{V_o}{V_i} = -\frac{C_s}{C_f} \cdot \frac{1 - S\frac{C_f}{g_m}}{1 + S\frac{C_L + C_f(1 - F)}{F \cdot g_m}}$$

(3.10)

$$F = \frac{C_f}{C_f + C_s + C_p} \tag{3.11}$$

Figure 3.7: Small-signal model of a capacitive-feedback amplifier

In Eq. 3.10, there is a pole determined by the transconductance  $(g_m)$  of the amplifier and the effective output capacitance, and a feedthrough zero. For a step input, the circuit response is given in Eq. 3.12 and 3.13.

$$V_{o,step}(t) = -V_{i,step} \cdot \frac{C_s}{C_f} \left\{ 1 - \left( 1 + \frac{P}{Z} \right) \exp^{-t/\tau} \right\}$$

(3.12)

$$P = -\frac{1}{\tau} = -\frac{F \cdot g_m}{C_L + C_f (1 - F)}, Z = \frac{g_m}{C_f}$$

(3.13)

The "(1+P/Z)exp<sup>-t/t</sup>" term indicates the relative settling error, and it is a constant determined by the bandwidth of the Opamp. The integrator gain error is often tolerable in the design of delta-sigma modulators, but not in the MASH architectures. It has been shown that finite bandwidth also causes the integrator leakage if finite gain effect is included [Sansen99], but that is quite small and can be omitted for hand analysis [Gustavsson00]. As long as the settling is linear, the required settling accuracy can be significantly lower than the accuracy of the delta-sigma ADC.

Therefore, a relatively low speed Opamp may be employed in the delta-sigma ADC for achieving higher power efficiency.

For small input step, the initial rate of change of the output voltage is proportional to the nominal steady-state output voltage:  $|V_{o,step}|/\tau$ . If it is smaller than the slew rate (SR), linear settling can be assumed for the whole period. For large input step,  $|V_{o,step}|/\tau$  may be greater than the SR, then the output voltage changes in a constant rate. If the output voltage reaches a point where  $\Delta V/\tau$  equals the slew rate  $(\Delta V=|V_{o,step}-V(t)|)$ , the Opamp would then enter the linear settling region. In case the input step is so large that  $\Delta V/\tau$  is always greater than the SR, the Opamp would be in the nonlinear settling region for the whole period [Wooley94]. The three cases are summarized in Eq. 3.14, 3.15, and 3.16, where  $T_s$  refers to the given settling time.

$|V_{o,step}| < SR*\tau$  (Linear settling):

$$V_{o,final} = V_{o,step} \left\{ 1 - \left( 1 + \frac{P}{Z} \right) \exp^{-\frac{T_s}{\tau}} \right\}$$

(3.14)

$SR*\tau < |V_{o,step}| < SR(\tau + T_s)$  (Weakly nonlinear settling):

$$V_{o,final} = V_{o,step} - \operatorname{sgn}\left(V_{o,step}\right) \cdot SR \cdot \tau \left(1 + \frac{P}{Z}\right) \exp^{\left[1 + \frac{T_s}{\tau} - \frac{\left|V_{o,step}\right|}{\tau^2}\right]}$$

(3.15)

$|V_{o,step}| > SR(\tau + T_s)$  (Nonlinear settling):

$$V_{o, final} = \operatorname{sgn}(V_{o, step}) \cdot T_s \cdot SR \tag{3.16}$$

Fig. 3.8 illustrates the different settling regions in terms of the nominal steadystate output voltage. In order to minimize harmonic distortion, it is important to limit the input and output voltage swings of the Opamp and keep it from operating in the slew-rate limiting regions.

Figure 3.8: Three settling regions in terms of the nominal output voltage

### 3. Gain nonlinearity

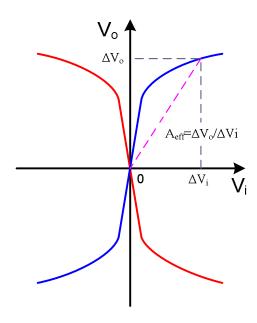

In this section, the amplifier gain nonlinearity will be investigated, and its effects on the in-band noise floor and harmonic distortion of delta-sigma modulators will be highlighted. Fig. 3.9 shows the typical DC transfer curve of an amplifier. When the input/output swing is small, the amplifier is operating in the high gain region. When the input/output swing is large, the output level becomes saturated and the gain of the amplifier will drop. As a result, the low frequency noise notch will be effectively widened and the actual in-band noise floor is raised up.

Figure 3.9: Typical amplifier transfer characteristics

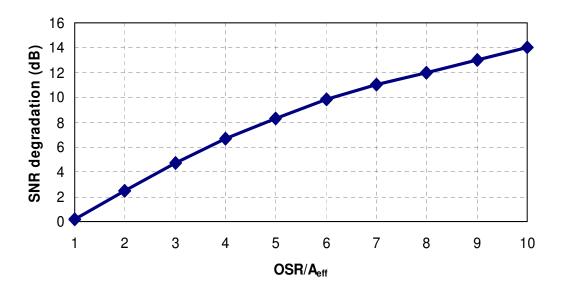

Due to the chaotic nature of the delta-sigma modulator, it's nontrivial to find an analytical solution for the nonlinear time-varying problem. To simplify the analysis, the effective gain  $(A_{eff})$  of the amplifier can be defined as the ratio of the maximum output voltage of the SC integrator to the corresponding input voltage of the amplifier. This represents the worst case. The additional quantization noise can be estimated by integrating  $|NTF(\omega)|^2 \approx A_{eff}^2 + \omega^2$  from DC to  $\pi/OSR$  and comparing the result against the  $A_{eff} = \infty$  case. Eq. 3.17 and 3.18 show the derivation. From this simple model, the SNR degradation can be plotted in terms of OSR/ $A_{eff}$ , shown in Fig. 3.10. For  $A_{eff} = OSR$ , the SNR degradation is only 0.2 dB, as mentioned previously. For  $A_{eff} < OSR/6$ , the SNR degradation can be more than 10 dB, which is phenomenal.

$$\Delta Q_e^2 = \int_0^{\frac{\pi}{OSR}} \left( A_{eff}^{-2} + \omega^2 \right) d\omega$$

$$= \frac{\pi}{A_{eff} OSR} + \frac{\pi^3}{3OSR^3}$$

(3.17)

$$\Delta SNR = 10\log_{10}\left(1 + \frac{3OSR^2}{A_{eff}^2\pi^2}\right) - 1$$

(3.18)

Figure 3.10: SNR degradation and the effective amplifier gain

In addition to raising the in-band noise floor, the amplifier gain nonlinearity also greatly contributes to the harmonic distortion in the SC integrator, which lowers the SNDR (including distortion tones) of the modulator for large input signals. The amplifier' gain characteristics can be approximated using a Volterra series [Yuan01], a hyperbolic tangent (tanh) function [Razavi06], or a variable-gain model [Yavari07]. However, the nonlinear gain estimation in the SC integrator is an iterative recursive procedure, so there is no simple analytical formula relating the harmonic outputs with

the nonlinear gain characteristics of the amplifier. Instead, the nonlinear model of the SC circuits can be implemented in a numerical simulator such as Matlab to estimate the harmonic distortions.

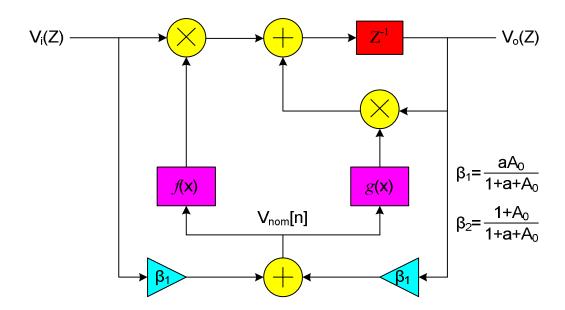

To further simplify the problem, a three-step procedure may be utilized [Yavari07]: first, the nominal output voltage  $V_{nom}[n]$  of a SC integrator is predicted using the small-signal DC gain  $A_0$ ; then, the large-signal DC gain  $A_{dc}(V_{nom}[n])$  is calculated based on the predicted output voltage. The relationship between  $A_0$  and  $A_{dc}(V_{nom}[n])$  is given in Eq. 3.19 and 3.20, where  $\alpha$  and  $\beta$  serve as the curve-fitting parameters in the nonlinear gain model; finally, the actual output voltage  $V_0[n]$  of the SC integrator is calculated based on  $A_{dc}(V_{nom}[n])$ , as shown in Eq. 3.21, 3.22, and 3.23. Fig. 3.11 shows a system-level model of the SC integrator, implementing the above procedures. It is seen that the nonlinear gain characteristics of the amplifier clearly affects the harmonic distortion of the SC integrator, hence the SNDR performance of the modulator.

$$V_{nom}[n] = \frac{1 + A_0}{1 + a + A_0} V_o[n-1] + \frac{aA_0}{1 + a + A_0} V_i[n-1]$$

(3.19)

$$A_{dc}\left(V_{nom}[n]\right) = A_0 \left(1 - \alpha \left| \frac{V_{nom}[n]}{V_{o,\text{max}}} \right|^{\beta} \right)$$

(3.20)

$$f(V_{nom}[n]) = \frac{a \cdot A_0 \left(1 - \alpha \left| \frac{V_{nom}[n]}{V_{o,\text{max}}} \right|^{\beta} \right)}{1 + a + A_0 \left(1 - \alpha \left| \frac{V_{nom}[n]}{V_{o,\text{max}}} \right|^{\beta} \right)}$$

(3.21)

$$g\left(V_{nom}[n]\right) = \frac{1 + A_0 \left(1 - \alpha \left| \frac{V_{nom}[n]}{V_{o,\text{max}}} \right|^{\beta}\right)}{1 + a + A_0 \left(1 - \alpha \left| \frac{V_{nom}[n]}{V_{o,\text{max}}} \right|^{\beta}\right)}$$

(3.22)

$$V_{o}[n] = g(V_{nom}[n]) \cdot V_{o}[n-1] + f(V_{nom}[n]) \cdot V_{i}[n-1]$$

(3.23)

Figure 3.11: Modeling the amplifier gain nonlinearity in a delaying SC integrator

# **B. Noise Sources**

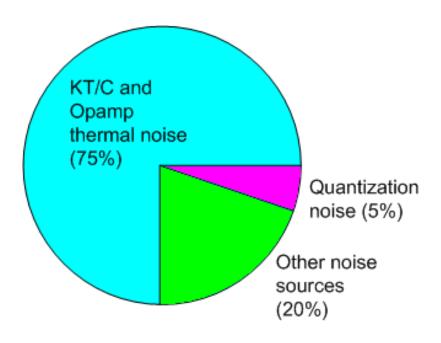

In addition to the quantization noise, there are also other noise sources in the delta-sigma modulator, such as KT/C noise, OPAMP noise, and jitter noise, affecting the achievable SNR performance of the modulator. Due to the possible signal-dependence of the quantization noise, it is important to minimize its contribution to the overall in-band noise power for achieving lower nonlinear distortion. The KT/C and Opamp thermal noise, which have a white spectrum, hence dominate the in-band noise floor for design optimization. Fig. 3.12 shows a typical noise budget in SC-based delta-sigma modulators.

Figure 3.12: Noise budget of the delta-sigma modulator

### 1. Thermal noise

Due to the Brownian motion of thermally-agitated charge carriers, any electrical conductor, such as a resistor or the conducting channel of a MOS device, exhibits an additive noise voltage at its terminals no matter there is DC current flow or not [Gray04]. In SC circuits, thermal noise manifests itself as the KT/C noise (or the switching noise) and Opamp thermal noise. It is helpful to analyze the noise process and quantify its contribution to the SNR performance of the modulator.

Figure 3.13: Small-signal models for thermal noise calculation

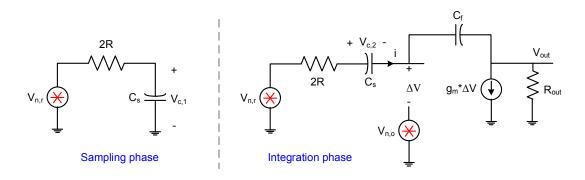

Fig. 3.13 shows the small-signal models for thermal noise calculation in the SC integrator. The conducting channel of a MOS switch is modeled as a resistor R, controlled by the gate-source voltage of the MOS device in the linear mode. It will be shown that the value of R has little effect on the resulting input-referred noise voltage. It's the size of the sampling capacitor ( $C_s$ ) that determines the in-band noise floor.

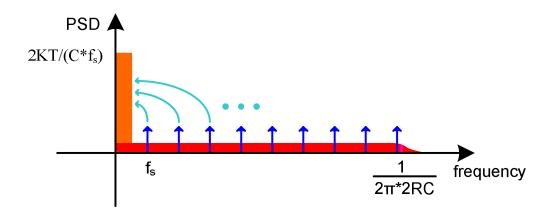

During the sampling phase, the SC circuit is modeled as an equivalent first-order RC filter. The noise power of the channel  $(\overline{V_{n,r}^2})$  is given by Eq. 3.24. Theoretically, thermal noise has a finite PSD from DC to infinite frequency, implying infinite noise

voltage at the terminals. After considering the filtering effect of the capacitor, it can be shown that the actual noise power on top of the capacitor is independent of the resistance, and occupies a spectrum from DC to the -3dB frequency ( $f_{-3dB}$ ) of the RC filter, as shown in Fig. 3.14.

In practice,  $f_{\text{-3dB}}$  is usually designed 10 times larger than the clock frequency for the SC circuit to achieve sufficient settling accuracy. Due to the inherent noise folding, the sampling process mixes the high frequency noise down to baseband, and the total in-band noise power on top of the capacitor  $(\overline{V_{c,1}^2})$  during the sampling phase is therefore equal to KT/C/OSR. Hence, it's called the KT/C noise.

$$\overline{V_{n\,r}^2} = 4KT \cdot 2R \cdot \Delta f \tag{3.24}$$

$$\overline{V_{c,1}^2} = 4KT \cdot 2R \cdot \frac{\pi}{2} \cdot \frac{1}{2\pi \cdot 2RC} \cdot \frac{1}{OSR} = \boxed{\frac{KT}{C \cdot OSR}}$$

(3.25)

Figure 3.14: Noise folding during the sampling phase

During the integration phase, the situation is slightly more complex since the circuit has a DC supply, implying thermal unequilibrium. From the knowledge of thermal dynamics, any capacitor (C) at thermal equilibrium has an average energy of KT/2, which translates to  $\overline{V_c^2}$  = KT/C. In case of thermal unequilibrium, the noise voltage on the capacitor can be derived in terms of both  $V_{n,r}$  and  $V_{n,o}$ , and the derivation is shown in Eq. 3.26 assuming infinite  $R_{out}$ . The in-band noise power on the capacitor ( $\overline{V_{c,2}^2}$ ) during the integration phase is shown in Eq. 3.27, considering the oversampling effect. The constant  $\lambda$  depends on the amplifier topology and the specific fabrication process, and it is usually 2-5 for short-channel devices.

$$(V_{n,r} - i \cdot 2R - V_{c2} - V_{n,o}) \cdot g_m = i = V_{c2} \cdot SC_s$$

$$\Rightarrow V_{c2} = \frac{V_{n,r} - V_{n,o}}{1 + SC_s \left(\frac{1}{g_m} + 2R\right)}$$

(3.26)

$$\overline{V_{c,2}^{2}} = \left(4KT \cdot 2R + 4KT \cdot \frac{\lambda}{g_{m}}\right) \cdot \frac{\pi}{2} \cdot \frac{1}{2\pi \cdot 2RC_{s} \left(1 + \frac{1}{2R \cdot g_{m}}\right)} \cdot \frac{1}{OSR}$$

$$\Rightarrow \overline{V_{c,2}^{2}} = \left[\frac{KT}{C_{s} \cdot OSR} \cdot \frac{\lambda + 2R \cdot g_{m}}{1 + 2R \cdot g_{m}}\right] \tag{3.27}$$

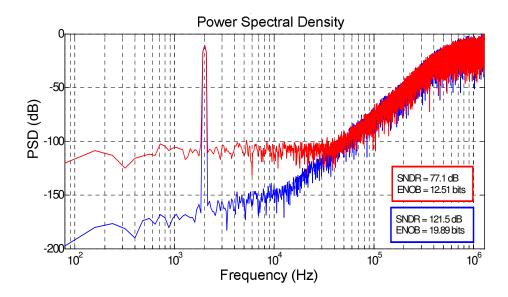

In Eq. 3.28, the quantities  $\overline{V_{c,1}^2}$  and  $\overline{V_{c,2}^2}$  are summed to find the total inputreferred in-band thermal noise power. It turns out that the in-band thermal noise of the SC integrator can be roughly modeled with a capacitor  $C_s/2$  at thermal equilibrium. Fig. 3.15 shows the output spectrums of a SC delta-sigma modulator with the KT/C noise (red) and without the KT/C noise (blue). It is clearly seen that the in-band noise floor is dominated by the KT/C noise and the high frequency spectrum is dominated by the quantization noise. For an OSR of 128, a 0.2 pF capacitor produces an in-band noise voltage of 40  $\mu$ V, which gives a maximum SNR of 82 dB for a 1.5 V reference voltage. To achieve better resolution, the sampling capacitor can be increased accordingly, but this would also affect the power consumption of the system, clock frequency, and silicon overhead. Thus, the choice of  $C_s$  is a tradeoff.

$$\overline{V_c^2} = \overline{V_{c,1}^2} + \overline{V_{c,2}^2} = \boxed{\frac{2KT}{C_s \cdot OSR} \cdot \left(1 + \frac{1}{2} \cdot \frac{\lambda - 1}{1 + 2R \cdot g_m}\right)}$$

(3.28)

Figure 3.15: KT/C noise versus quantization noise

# 2. Clock jitter

Another major noise source is clock jitter. Clock jitter refers to the temporal variation of the clock period at a given point, which is measured on a cycle-to-cycle basis and can be modeled as a random variable. On the contrary, clock skew refers to the spatial variation in the arrival time of a clock transition, which is a static quantity [Rabaey02]. Table 3.1 compares clock jitter and clock skew in terms of characteristics, impacts, and sources. In digital circuits, both jitter and skew affects the maximum frequency of operation; in analog circuits, such as the SC integrator, jitter is a more important measure since it limits the sampling accuracy of the clock signal.

Table 3.1: Clock jitter versus clock skew

|        | Characteristics     | Impacts              | Sources                  |

|--------|---------------------|----------------------|--------------------------|

|        | Temporal variation, | Always degrade the   | Clock-signal generation, |

| Jitter | Dynamic quantity,   | clocking accuracy    | Power supply variation,  |

|        | Random error        |                      | Capacitive coupling      |

|        | Spatial variation,  | Depends on the       | Device mismatch,         |

| Skew   | Static quantity,    | direction of skew:   | Interconnect mismatch,   |

|        | Systematic error    | positive or negative | Temperature variation    |

|        |                     |                      |                          |

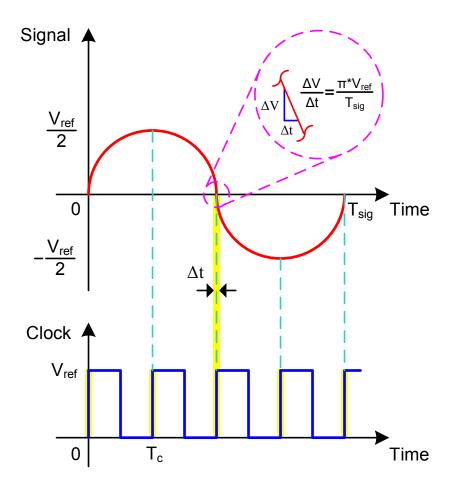

Fig. 3.16 shows the sampling diagram consisting of a sinusoidal input signal and a jittery clock. According to the central limit theorem, clock jitter is a summation of many small random variables, thus it has a probability density function (PDF) of

Gaussian distribution with zero mean value. The quantity  $\Delta t$  is the standard deviation ( $\sigma$ ) of the Gaussian PDF. When the sampling clock is jittery, the actual sampled voltage differs from the ideal voltage at the nominal sampling instant, and the voltage difference  $\Delta V$  is determined by the slope of the signal waveform and the time deviation  $\Delta t$ . Since a sinusoidal waveform has maximum slope at the zero-crossings, the maximum slope can be used to predict the worst-case jitter-induced noise voltage.

Eq. 3.29 and 3.30 shows the derivation of  $\Delta V$  and the maximum SNR of the oversampling ADC considering only jitter noise, respectively. The SNR<sub>max</sub> is determined by the ratio of the signal period  $T_{sig}$  and the clock jitter  $\Delta t$ . Since the sampling happens before the integration, the jitter noise will not be high-pass filtered by the modulator. In reality, the jitter-induced SNR<sub>max</sub> should be kept at least 10 dB higher than the target SNR performance of the ADC, and the input KT/C noise still dominates.

$$\Delta V = \Delta t \cdot \frac{\partial \left[ \frac{V_{ref}}{2} \sin \left( \omega_{sig} t \right) \right]}{\partial t} = \frac{\Delta t \cdot \pi \cdot V_{ref}}{T_{sig}}$$

(3.29)

$$SNR_{\text{max}} = 20\log_{10}\left(\frac{V_{sig}}{V_{noise}}\right) = 20\log_{10}\frac{V_{ref}/(2\sqrt{2})}{\Delta V/\sqrt{OSR}}$$

$$\approx \left[-19 + 20\log_{10}\left(\frac{T_{sig}}{\Delta t}\sqrt{OSR}\right)\right]$$

(3.30)

Figure 3.16: Sampling diagram with clock jitter

### C. Distortion Sources

Aside from the random noise sources, nonlinear response of SC circuits would produce harmonic distortions in the output spectrum, and this deterministic error degrades the SNDR performance of the modulator especially for large input signals. Depending on specific applications, such as an audio codec, the harmonic distortion may be a more serious concern than the random noises.

As discussed in previous sections, amplifier gain nonlinearity and slew-rate limiting effect are the major factors for the harmonic distortion in SC circuits. In this section, additional distortion sources will be analyzed at both the system and circuit levels and their specific contributions to the nonlinear tones will be identified.

# 1. Mismatch in the differential paths

The symmetry of fully differential amplifiers tends to cancel out the even-order harmonic terms in the transfer function. Eq. 3.31 gives the transfer function of a single-ended amplifier in the Volterra series, from which the transfer function of a differential amplifier can be derived, as shown in Eq. 3.32. It is noted that the even-order harmonics are eliminated since they have the same amplitude and polarity at both the positive and negative outputs. For a sinusoidal input ( $\omega_{sig}$ ), the output spectrum contains both the fundamental tone ( $\omega_{sig}$ ) and odd-order harmonic tones ( $3\omega_{sig}$ ,  $5\omega_{sig}$ , and  $7\omega_{sig}$  ...) decreasing in amplitude, and ideally no even-order harmonic tones ( $2\omega_{sig}$ ,  $4\omega_{sig}$ , and  $6\omega_{sig}$  ...) would show up. This holds true for other fully-differential circuits as well, such as SC circuits.

$$y_{sa}(x) = a_1 x + a_2 x^2 + a_3 x^3 + a_4 x^4 + a_5 x^5 + \cdots$$

(3.31)

$$y_{diff}(x) = y\left(\frac{x}{2}\right) - y\left(-\frac{x}{2}\right) = a_1 x + a_3 \frac{\left(x\right)^3}{4} + a_5 \frac{\left(x\right)^5}{16} + \cdots$$

(3.32)

Due to fabrication resolution, DC offset, and voltage dependence of the components, however, there are no ideally fully-differential circuits in reality. In a standard 0.13 µm CMOS process, a 100 µm by 100 µm MIM capacitor has an absolute error of 0.5% and a mismatch error of 0.05%. For smaller on-chip capacitors, the errors would be bigger. In addition, the use of on-chip resistor is usually avoided in the signal path since its value is even more loosely controlled.

Considering these mismatch effects in the differential paths, the actual transfer function of a differential amplifier would contain finite even-order harmonic tones, as shown in Eq. 3.33, where  $\Delta a_2$  and  $\Delta a_4$  model the difference in the even-order coefficients  $a_2$  and  $a_4$ .

$$y_{diff}(x) = a_1 x + \Delta a_2 \frac{(x)^2}{2} + a_3 \frac{(x)^3}{4} + \Delta a_4 \frac{(x)^4}{8} + a_5 \frac{(x)^5}{16} + \cdots$$

(3.33)

#### 2. Even-order harmonic distortion

In the previous section, the generation of  $\Delta a_2$  and  $\Delta a_4$  terms is explained and related to the differential path mismatch. However, that is only the necessary condition for the even-order harmonic distortion, not the sufficient one. This section discusses the actual generation of the even-order coefficients  $a_2$  and  $a_4$ .

Intuitively, the even-order harmonic terms results from the signal-dependence of electrical components or the voltage references along the signal path. One of the major contributory factors is the nonlinearity of sampling capacitors. Due to the voltage-induced polarization of dielectric, on-chip capacitors have non-zero voltage-coefficient depending on the structure. In some circuits such as the VCO, a variable capacitor (Varactor) is needed to tune the oscillation frequency, and the voltage-dependence is desired. In many other cases, such as the SC circuits, the voltage dependence causes the undesired even-order harmonic terms. Eq. 3.34 shows the simplified model of a nonlinear capacitor, and Eq. 3.35 shows the resulting transfer function of a SC amplifier based on the nonlinear capacitor, assuming all the other factors ideal. Clearly, there is a 2<sup>nd</sup>-order term in the transfer function.

$$C_s(V) = C_0 + C_1 V (3.34)$$

$$y(x) = \frac{x \cdot C_s(x)}{C_f} = \frac{C_0}{C_f} x + \frac{C_1}{C_f} x^2$$

(3.35)

Another major distortion source belongs to the signal-dependent feedback voltages, though it is more subtle. In a single-bit quantizer, for example, the two voltage levels are related to the power supplies. The power supplies might slightly rise or fall as the modulator draws more or less current from the supply for different input amplitudes, therefore the two output levels somehow become a function of the input signals that they are being used to represent. In addition, this supply variation may also cause the charge injection of MOS switches signal-dependent as well, since the clock signals are also derived from the power supplies. Therefore, it is important

to have well-regulated power supplies on both the quantizer and buffers for the clock signals.

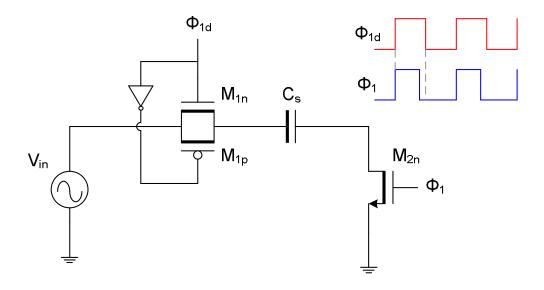

#### 3. Nonideal switches

It is worthwhile to investigate the limitations of MOS switches more carefully. Fig. 3.17 shows the input sampling circuit and the associated timing diagram. In the sampling phase, the MOS switches  $M_{1n}$  and  $M_{1p}$  are operating in the linear mode, and the channel charges can be given by Eq. 3.36 and 3.37. The total channel charges of the input switches can be calculated as shown in Eq. 3.38, assuming  $M_{1n}$  and  $M_{1p}$  have the same size. When the input switches are closed, the channel charges go in two directions: the signal source (harmless) and the sampling capacitor. The divide ratio is a complex function of the instantaneous input voltage [Wegmann87]. In addition, the threshold voltages  $V_{tn}$  and  $|V_{tp}|$  are also a nonlinear function of the input voltage, due to the body effect. Therefore, the nonlinearity in the circuit is also related to the signal-dependent charge injection from the input switches.

$$Q_{1n} = -C_{ox} (WL)_{1n} (V_{dd} - V_{in} - V_{ln})$$

(3.36)

$$Q_{1p} = C_{ox} (WL)_{1p} (V_{in} - |V_{ip}|)$$

(3.37)

$$Q_{1} = C_{ox} (WL)_{1} (2V_{in} + V_{tn} - |V_{tp}| - V_{dd})$$

(3.38)

Figure 3.17: Input sampling circuitry of SC circuits

To mitigate this problem, the bottom-plate sampling technique can be utilized: the switch  $M_{2n}$  is turned off slightly earlier than the switch  $M_1$ . By turning  $M_{2n}$  off earlier, the capacitor  $C_s$  becomes a high-impedance node and all of  $Q_1$  would go to the signal source. Since the terminal voltages of  $M_{2n}$  are fixed in the steady-state, its charge injection only causes a constant offset and can be calibrated out. In reality, the charge injection from  $M_{2n}$  also depends on the channel conductance of  $M_1$ , which is also a nonlinear function of the input signal. Thus, the switch  $M_{2n}$  may also contribute to the output harmonic distortion in the SC circuit.

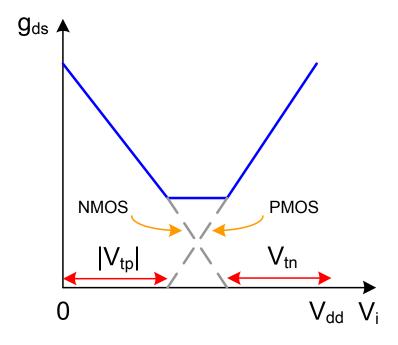

Figure 3.18: Conductance of a transmission gate switch

Fig. 3.18 shows the voltage dependence of the channel conductance of MOS switches, formed by a CMOS transmission gate [Abo99]. The channel conductance determines the time constant of the input sampling circuit, which becomes a function of voltage. If the bandwidth of the input circuit is low, the signal-dependent time constant would give rise to large distortion, and this distortion also increases with the signal frequency. It is therefore important to have sufficiently large switch conductance to avoid this problem.

# IV. SYSTEM CONSIDERATIONS

After elaborating the relevant circuit nonlinearities in the ADC design, the system architectures will be discussed in this chapter in different aspects, pertaining to the micro power delta-sigma modulator design in the dissertation.

# A. Delta-Sigma versus Nyquist-Rate